ADXL180WCPZ-RL Analog Devices Inc, ADXL180WCPZ-RL Datasheet - Page 23

ADXL180WCPZ-RL

Manufacturer Part Number

ADXL180WCPZ-RL

Description

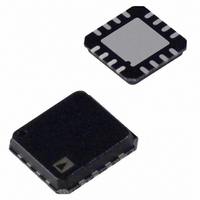

IC ACCELEROMETER CONFIG 16-LFCSP

Manufacturer

Analog Devices Inc

Series

iMEMS®r

Datasheet

1.ADXL180WCPZ-RL.pdf

(60 pages)

Specifications of ADXL180WCPZ-RL

Axis

X or Y

Acceleration Range

±50g, 100g, 150g, 200g, 250g, 350g, 500g

Voltage - Supply

5 V ~ 14.5 V

Output Type

Analog

Bandwidth

100Hz ~ 800Hz Selectable

Mounting Type

Surface Mount

Package / Case

16-LFQFN, CSP Exposed Pad

Package Type

LFCSP EP

Operating Supply Voltage (min)

5V

Operating Temperature (min)

-40C

Operating Temperature (max)

125C

Operating Temperature Classification

Automotive

Product Depth (mm)

5mm

Product Height (mm)

1.43mm

Product Length (mm)

5mm

Mounting

Surface Mount

Pin Count

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Sensitivity

-

Interface

-

Lead Free Status / Rohs Status

Compliant

Other names

ADXL180WCPZ-RLCT

DATA FRAME DEFINITION

DATA FRAME TRANSMISSION FORMAT

A data frame starts with two start bits. The value of these two

bits is determined by the Manchester encoding mode select bit.

See the Manchester Data Encoding section. Figure 19 shows the

basic format and timing of the data frame. A 1-bit idle time is

an implicit stop bit at the end of a data frame.

DATA FRAME CONFIGURATION OPTIONS

Figure 20 diagrams the protocol data frame construction

options. The data frame can be broken into four specific fields

as follows:

•

Start bits—two start bits are always transmitted at the start

of the data frame. These bits are used to synchronize the

center module decoder with the Manchester encoded signal.

MODULE DECODER

LOGIC SIGNAL

AT CONTROL

CURRENT

LOOP

0

0

I

IDLE

I

MOD

Figure 19. Data Message Timing (Manchester-1, Bit Coding)

START

t

BIT 0

B

START

BIT 0

‘1’

START

BIT 1

START

BIT 1

‘0’

Rev. A | Page 23 of 60

t

•

•

•

Depending on the settings of the configuration register bits

(ERC, SVD, and DAT), the data frame can be from 11 bits to

18 bits in length. Figure 20 shows the formats of the available

data frames. Note that the error checking field is transmitted

first when the CRC is selected but transmitted last when parity

is selected. See Figure 20 for specific examples of full protocol

configurations.

TIME

M

DATA BITS

Error checking—a single parity bit or a 3-bit CRC code can

be selected.

State vector—identifies the type of data in the data field. It

can be disabled. When it is disabled, it is not transmitted.

Data—the device data and sensor data can be transmitted

in either 8-bit or 10-bit mode.

DATA BITS

ADXL180