ADXL180WCPZ-RL Analog Devices Inc, ADXL180WCPZ-RL Datasheet - Page 11

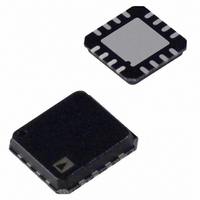

ADXL180WCPZ-RL

Manufacturer Part Number

ADXL180WCPZ-RL

Description

IC ACCELEROMETER CONFIG 16-LFCSP

Manufacturer

Analog Devices Inc

Series

iMEMS®r

Datasheet

1.ADXL180WCPZ-RL.pdf

(60 pages)

Specifications of ADXL180WCPZ-RL

Axis

X or Y

Acceleration Range

±50g, 100g, 150g, 200g, 250g, 350g, 500g

Voltage - Supply

5 V ~ 14.5 V

Output Type

Analog

Bandwidth

100Hz ~ 800Hz Selectable

Mounting Type

Surface Mount

Package / Case

16-LFQFN, CSP Exposed Pad

Package Type

LFCSP EP

Operating Supply Voltage (min)

5V

Operating Temperature (min)

-40C

Operating Temperature (max)

125C

Operating Temperature Classification

Automotive

Product Depth (mm)

5mm

Product Height (mm)

1.43mm

Product Length (mm)

5mm

Mounting

Surface Mount

Pin Count

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Sensitivity

-

Interface

-

Lead Free Status / Rohs Status

Compliant

Other names

ADXL180WCPZ-RLCT

SIGNAL PROCESSING

The ADXL180 contains an on-board set of signal processing

blocks both prior to and after ADC conversion. The first stage is

a fully differential, switched capacitor, low-pass, three-pole

Bessel filter. Range scaling is also handled in one of the filter

blocks, enabling 50 g to 500 g range capability. At this point, an

analog output test signal (V

diagnostic mode. The signal then converts by a 10-bit rail-to-rail

SAR ADC. In the digital section, an auto-zero routine is

available to the user as part of the state machine in addition to

error detection features such as offset drift detection.

DIGITAL COMMUNICATIONS STATE MACHINE

The ADXL180 digital state machine is based on a Core 5 phase

state machine implemented in high density CMOS. This state

machine handles the sequential states of

Phase 1. Initialization.

Phase 2. Device data transmission, including individual serial

Phase 3. Self-diagnostic, including automatic full electro-

Phase 4. Auto-zero initialization, if selected. During this phase,

Phase 5. Normal acceleration data transmission.

2-WIRE CURRENT MODULATED INTERFACE

The data that is generated during these five phases is trans-

mitted using a 2-wire high voltage communication port. This

allows the device to be powered by a fixed supply voltage, and

communicate back to the system or ECU electronics by modulating

current. Current modulated messages are encoded using Man-

chester encoding.

Table 5. Factory Programmed and User-Programmed Memory

Programmed By

User

Factory

number and user-programmed data.

mechanical self-test with internal error detection

available.

acceleration data is already available.

Configuration Mode

Register Address

0000b

0001b

0010b

0011b

1011b

1100b

1101b

1110b

1111b

SCO

) is available to the user in a

Configuration Mode

Register Name

UREG

CREG0

CREG1

CREG2

SN0

SN1

SN2

SN3

MFGID

Rev. A | Page 11 of 60

MSB

D7

UD7

UD8

STI

CUPRG CUPAR SCOE

SNB7

SNB15 SNB14 SNB13 SNB12 SNB11 SNB10

SNB23 SNB22 SNB21 SNB20 SNB19 SNB18

SNB31 SNB30 SNB29 SNB28 SNB27 SNB26

SNPRG SNPAR REV2

SYNCHRONOUS OPERATION AND DUAL DEVICE

BUS

In a point-to-point bus topology, the ADXL180 supports asyn-

chronous transmission of data to the receive device every 228 μs,

controlled by the on-board state machine. A synchronous option

is also available, allowing two devices to be on the same bus

using time division multiplexing where each device transmits its

data during a known time slot.

Synchronization is achieved by voltage modulated synchronization

pulses, configuring the ADXL180 device into a synchronous

mode, and establishing data frame time slots. The high voltage

communication port registers valid synchronization pulses and

enables message-by-message advancement of the state machine

rather than asynchronous timed regular data transmission.

PROGRAMMED MEMORY AND CONFIGURABILITY

Factory-Programmed Serial Number and Manufacturer

Information

The ADXL180 includes a 32-bit factory-programmed serial

number, as shown in Table 5. This serial number transmits

during Phase 2 of startup for all devices to enable robust quality

tracking of individual devices, and it is field readable. In addition,

this data includes revision information and manufacturer identi-

fication in case multiple devices used within a single application

are from different manufacturers or generations of parts.

User-Programmable Data Register

The ADXL180 gives the user an 8-bit register of user-program-

mable data, which is transmitted during Phase 2 of the state

machine. In addition, the UD8 bit, a ninth user-available bit,

is transmitted separately during Phase 2 and can be used for

various purposes, such as orientation definition or module type.

D6

UD6

BDE

AZE

SNB6

D5

UD5

MD1

SYEN

SNB5

D4

UD4

MD0

FC1

SNB4

REV1

ADME ERC

D3

UD3

FDLY

FC0

SNB3

REV0

D2

UD2

DLY2

SVD

RG2

SNB2

MFGID2 MFGID1 MFGID0

D1

DLY1

UD1

DAT

RG1

SNB1

SNB9

SNB17

SNB25

ADXL180

LSB

D0

UD0

DLY0

RG0

SNB0

SNB8

SNB16

SNB24

MAN