ADXL180WCPZ-RL Analog Devices Inc, ADXL180WCPZ-RL Datasheet - Page 21

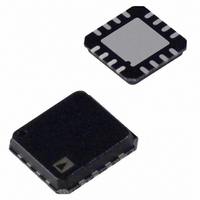

ADXL180WCPZ-RL

Manufacturer Part Number

ADXL180WCPZ-RL

Description

IC ACCELEROMETER CONFIG 16-LFCSP

Manufacturer

Analog Devices Inc

Series

iMEMS®r

Datasheet

1.ADXL180WCPZ-RL.pdf

(60 pages)

Specifications of ADXL180WCPZ-RL

Axis

X or Y

Acceleration Range

±50g, 100g, 150g, 200g, 250g, 350g, 500g

Voltage - Supply

5 V ~ 14.5 V

Output Type

Analog

Bandwidth

100Hz ~ 800Hz Selectable

Mounting Type

Surface Mount

Package / Case

16-LFQFN, CSP Exposed Pad

Package Type

LFCSP EP

Operating Supply Voltage (min)

5V

Operating Temperature (min)

-40C

Operating Temperature (max)

125C

Operating Temperature Classification

Automotive

Product Depth (mm)

5mm

Product Height (mm)

1.43mm

Product Length (mm)

5mm

Mounting

Surface Mount

Pin Count

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Sensitivity

-

Interface

-

Lead Free Status / Rohs Status

Compliant

Other names

ADXL180WCPZ-RLCT

Configuring Synchronous Operation

Delay Selection

As shown in Table 9, the user can select the data timing of the

second device to establish the predefined data slots. This allows

for the fastest possible sampling, if required, and Table 9 shows

the number of data frame bits the first device may transmit to

ensure no overlap. To further reduce device interference from

line or system circuit effects, use higher FDLY amounts than the

minimum.

Table 9. Data Transmission Delay Codes

DLY2

0

0

0

0

1

1

1

1

Fixed Delay Mode

Fixed delay mode establishes which device transmits in the

second time slot. FDLY requires that either (but not both) of

the two devices on the bus have the FDLY bit programmed to

enable the data frame transmission delay time. The device with

the FDLY bit set is named Device 2. Device 2 delays its data

transmission by the amount of time programmed into the

configuration register via Bit DLY2, Bit DLY1, and Bit DLY0.

After receiving a valid synchronization pulse, only Device 1,

without the FDLY bit set, sinks I

current (if the BDE bit is set) to return the V

nominal supply voltage.

Table 10. Fixed Delay Mode

FDLY

0

1

Caution: do not set Device 2 using Time Slot B as BDE = 1.

Only Device 1 should draw I

BDE bit is set. It is good practice to never have BDE = 1 and

FDLY = 1 in the same device.

Autodelay Mode

Table 11. Autodelay Mode Enable (ADME) Options

ADME

0

1

DLY1

0

0

1

1

0

0

1

1

Definition

Fixed delay mode disabled (default).

Fixed delay mode enabled. Device transmits data in the

time slot delayed by t

Definition

Autodelay mode is disabled. The part does not check

for a second device on the line and does not pull any

extra current during startup (default).

Autodelay mode detection is enabled. Pull down I

for 6 ms at power up.

DLY0

0

1

0

1

0

1

0

1

Delay Time

(t

205 μs

213 μs

221 μs

229 μs

237 μs

245 μs

253 μs

261 μs

DLY

SIG

)

DLY

as an active pull-down when the

SIG

as defined by DLY2 to DLY0.

as an active bus pull-down

Maximum First Data

Frame Bits

11

12

13

14

15

16

17

18

BP

voltage to the

DET

Rev. A | Page 21 of 60

The autodelay mode allows two identically configured devices

to be wired in a series configuration. The two devices automatically

configure the two node network upon power up. The configura-

tion bit (ADME) must be set to enable the autodelay mode. A

device with the ADME bit set sinks a bus current of I

upon power up.

The first device in the series configuration (Device 2) detects

the presence of the other device in the series (Device 1) by

sensing the I

Pin V

Phase 1. If the current draw of Device 1 is present, Device 2

delays its data transmission by the amount of time programmed

into the configuration register via Bit DLY2, Bit DLY1, and

Bit DLY0. Therefore, Device 2 transmits its data during Time

Slot B. The data transmission delay time of Device 2 is usually

selected based on the number of bits in the data frame. After

receiving a valid synchronization pulse, only Device 1 sinks I

as an active pull-down current (if the BDE bit is set) to return

the V

Time Slot B) never sinks I

BDE bit is set.

In a single device network, the unit that would be called Device 1

is not present. Therefore, the single device detects no current

draw through the V

this case, the single device transmits data during Time Slot A.

This allows a device programmed with a nonminimum delay

time to be used as either Device 1 or Device 2 in a series

configuration or as a single device.

The autodelay mode detect function samples the state of the

autodelay detect sense circuit every 500 μs during the first 6 ms

of Phase 1. A total of four consecutive samples must be valid to

place the device in the autodelay mode.

Caution: do not send an additional valid sync pulse during the

blanking period, t

the risk of the signal being misinterpreted and a change in

message response timing.

Dual Device Synchronous Parallel Topology

The two devices are wired in a parallel configuration as shown in

Figure 17. This configuration must be run in the fixed delay mode.

MODULE

CENTER

BP

BC

voltage to the nominal supply voltage. Device 2 (using

during the first 6 ms of the power-up initialization

Figure 17. Dual Device—Parallel Configuration

DET

current passing though itself from Pin V

V

STD

BP

BC

or t

V

pin during the power-on initialization. In

DEVICE 1

BN

B

, for either device, because it incurs

SIG

V

NC

BN

as an active pull-down even if the

V

NC

BC

V

BP

V

DEVICE 2

BN

ADXL180

V

NC

DET

BN

for 6 ms

V

BP

NC

BC

to

SIG