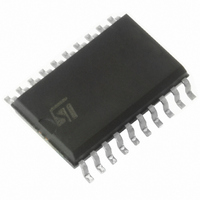

ST7FDALIF2M6 STMicroelectronics, ST7FDALIF2M6 Datasheet - Page 151

ST7FDALIF2M6

Manufacturer Part Number

ST7FDALIF2M6

Description

IC MCU 8BIT 8K 20-SOIC

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST7DALI-EVAL.pdf

(171 pages)

Specifications of ST7FDALIF2M6

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

DALI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

15

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

384 x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 5.5 V

Data Converters

A/D 7x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

20-SOIC (7.5mm Width)

Processor Series

ST7DALI

Core

ST7

Data Bus Width

8 bit

Data Ram Size

384 B

Interface Type

DALI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

15

Number Of Timers

4 bit

Operating Supply Voltage

2.4 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

ST7FLITE-SK/RAIS, ST7DALI-EVAL, ST7MDT10-DVP3, ST7MDT10-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit

For Use With

497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-2131-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST7FDALIF2M6TR

Manufacturer:

NEC

Quantity:

670

ST7DALIF2

20.10

20.10.1

RESET pin protection when LVD is disabled

When the LVD is disabled, it is recommended to protect the RESET pin as shown in

Figure 88

1.

2.

3.

4.

Figure 88. RESET pin protection when LVD is disabled.

Communication interface characteristics

SPI - serial peripheral interface

Subject to general operating conditions for V

Refer to I/O port characteristics for more details on the input/output alternate function

characteristics (SS, SCK, MOSI, MISO).

Table 88.

1/t

Symbol

Required

f

t

t

EXTERNAL

r(SCK)

SCK =

f(SCK)

CIRCUIT

c(SCK)

RESET

USER

The reset network protects the device against parasitic resets.

The output of the external reset circuit must have an open-drain output to drive the ST7

reset pad. Otherwise the device can be damaged when the ST7 generates an internal

reset (LVD or watchdog).

Whatever the reset source is (internal or external), the user must ensure that the level

on the RESET pin can go below the V

the reset will not be taken into account internally.

Because the reset circuit is designed to allow the internal RESET to be output in the

RESET pin, the user must ensure that the current sunk on the RESET pin (by an

external pull-up for example) is less than the absolute maximum value specified for

I

INJ(RESET)

SPI clock frequency

SPI clock rise and fall

time

and follow these guidelines:

SPI characteristics

Parameter

in

0.01μF

Section 20.2 on page

Master

Slave

Conditions

V

DD

f

f

CPU

CPU

128.

R

ON

IL

Filter

=8 MHz f

=8 MHz

DD

max. level specified in

, f

GENERATOR

OSC

PULSE

, and T

CPU

/128 =0.0625

Min

see I/O port pin description

A

0

unless otherwise specified.

Electrical characteristics

Section

WATCHDOG

ILLEGAL OPCODE

INTERNAL

RESET

f

f

CPU

CPU

Max

20.8. Otherwise

ST72XXX

/4 =2

/2 =4

151/171

MHz

Unit