ST72F262G2B5 STMicroelectronics, ST72F262G2B5 Datasheet - Page 109

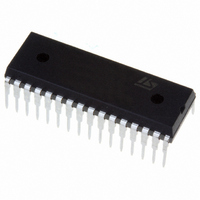

ST72F262G2B5

Manufacturer Part Number

ST72F262G2B5

Description

IC MCU 8BIT 8K FLASH 32-SDIP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.STEVAL-ISQ002V1.pdf

(172 pages)

Specifications of ST72F262G2B5

Core Processor

ST7

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

22

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-10°C ~ 85°C

Package / Case

32-SDIP (0.400", 10.16mm)

Processor Series

ST72F2x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

I2C, SCI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

22

Number Of Timers

16 bit

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

ST7F264-IND/USB, ST72F34X-SK/RAIS, ST7MDT10-DVP3, ST7MDT10-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F262G2B5

Manufacturer:

TAIYO

Quantity:

8 122

I

11.6.5 Low Power Modes

11.6.6 Interrupts

Figure 60. Event Flags and Interrupt Generation

Note: The I

the same interrupt vector (see Interrupts chapter).

They generate an interrupt if the corresponding

Enable Control Bit is set and the I-bit in the CC reg-

ister is reset (RIM instruction).

2

WAIT

HALT

10-bit Address Sent Event (Master mode)

End of Byte Transfer Event

Address Matched Event (Slave mode)

Start Bit Generation Event (Master mode)

Acknowledge Failure Event

Stop Detection Event (Slave mode)

Arbitration Lost Event (Multimaster configuration)

Bus Error Event

C BUS INTERFACE (Cont’d)

Mode

*

EVF can also be set by EV6 or an error from the SR2 register.

STOPF

ADD10

BERR

ARLO

ADSL

*

BTF

No effect on I

I

I

In HALT mode, the I

resumes operation when the MCU is woken up by an interrupt with “exit from HALT mode” capability.

2

2

SB

AF

2

C interrupts cause the device to exit from WAIT mode.

C registers are frozen.

C interrupt events are connected to

2

C interface.

Interrupt Event

2

C interface is inactive and does not acknowledge data on the bus. The I

ITE

Description

ST72260Gx, ST72262Gx, ST72264Gx

ADSEL

STOPF

ADD10

BERR

Event

ARLO

Flag

BTF

SB

AF

Control

Enable

ITE

Bit

INTERRUPT

EVF

from

Wait

Exit

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

2

C interface

109/172

from

Halt

Exit

No

No

No

No

No

No

No

No