T89C5115-TISUM Atmel, T89C5115-TISUM Datasheet - Page 35

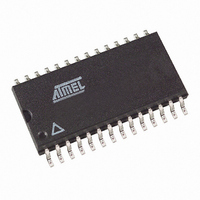

T89C5115-TISUM

Manufacturer Part Number

T89C5115-TISUM

Description

IC 8051 MCU FLASH 16K 28SOIC

Manufacturer

Atmel

Series

89Cr

Datasheet

1.T89C5115-RATIM.pdf

(113 pages)

Specifications of T89C5115-TISUM

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

20

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

2K x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-SOIC (7.5mm Width)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

89C5115-TISUM

- Current page: 35 of 113

- Download datasheet (2Mb)

Status of the Flash Memory

Selecting FM1

Loading the Column Latches

4128G–8051–02/08

The bit FBUSY in FCON register is used to indicate the status of programming.

FBUSY is set when programming is in progress.

The bit ENBOOT in AUXR1 register is used to map FM1 from F800h to FFFFh.

Any number of data from 1 byte to 128 Bytes can be loaded in the column latches. This

provides the capability to program the whole memory by byte, by page or by any number

of Bytes in a page.

When programming is launched, an automatic erase of the locations loaded in the col-

umn latches is first performed, then programming is effectively done. Thus no page or

block erase is needed and only the loaded data are programmed in the corresponding

page.

The following procedure is used to load the column latches and is summarized in

Figure 14:

•

•

•

•

•

•

Save then disable interrupt and map the column latch space by setting FPS bit.

Load the DPTR with the address to load.

Load Accumulator register with the data to load.

Execute the MOVX @DPTR, A instruction.

If needed loop the three last instructions until the page is completely loaded.

unmap the column latch and Restore Interrupt

35

Related parts for T89C5115-TISUM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC 8051 MCU FLASH 16K 32VQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC 8051 MCU FLASH 16K 28PLCC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC 8051 MCU FLASH 16K 24SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC 8051 MCU FLASH 16K 28SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Low Pin Count 8-bit MCU with A/D Converter and 16-Kbytes of Flash Memory

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: