R5F21134DFP#U0 Renesas Electronics America, R5F21134DFP#U0 Datasheet - Page 201

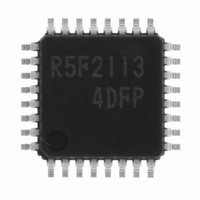

R5F21134DFP#U0

Manufacturer Part Number

R5F21134DFP#U0

Description

IC R8C MCU FLASH 32LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/R8C/Tiny/13r

Datasheets

1.R5F211A2SPU0.pdf

(300 pages)

2.R5F21132FPU0.pdf

(33 pages)

3.R5F21132FPU0.pdf

(226 pages)

4.R5F21134DFPU0.pdf

(224 pages)

Specifications of R5F21134DFP#U0

Core Size

16-Bit

Program Memory Size

16KB (16K x 8)

Oscillator Type

Internal

Core Processor

R8C

Speed

20MHz

Connectivity

SIO, UART/USART

Peripherals

LED, POR, Voltage Detect, WDT

Number Of I /o

22

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

No. Of I/o's

22

Eeprom Memory Size

4KB

Ram Memory Size

1024Byte

Cpu Speed

20MHz

No. Of Timers

16

Digital Ic Case

RoHS Compliant

Controller Family/series

R8C/13

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

R0K521134S000BE - KIT EVAL STARTER FOR R8C/13R0E521134EPB00 - KIT EMULATOR PROBE FOR PC7501R0E521134CPE00 - EMULATOR COMPACT R8C/13

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

R5F21134DFP#U0R5F21134DFP

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- R5F211A2SPU0 PDF datasheet

- R5F21132FPU0 PDF datasheet #2

- R5F21132FPU0 PDF datasheet #3

- R5F21134DFPU0 PDF datasheet #4

- Current page: 201 of 226

- Download datasheet (3Mb)

R8C/13 Group

Rev.1.20

REJ09B0111-0120

19.2 Interrupt

19.2.1 Reading Address 00000

19.2.2 SP Setting

19.2.3 External Interrupt and Key Input Interrupt

19.2.4 Watchdog Timer Interrupt

________

Do not read the address 00000

the CPU reads interrupt information (interrupt number and interrupt request level) from 00000

interrupt sequence. At this time, the acknowledged interrupt IR bit is set to “0”.

If the address 00000

among the enabled interrupts is set to “0”. This may cause a problem that the interrupt is canceled, or

an unexpected interrupt is generated.

Set any value in the SP before an interrupt is acknowledged. The SP is set to “0000

Therefore, if an interrupt is acknowledged before setting any value in the SP, the program may run out

of control.

Either an “L” level or an ”H” level of at least 250ns width is necessary for the signal input to the INT

INT

Reset the watchdog timer after a watchdog timer interrupt is generated.

Jan 27, 2006

3

pins and KI

_____

page 188 of 205

0

to KI

16

_____

3

is read by a program, the IR bit for the interrupt which has the highest priority

pins regardless of the CPU clock.

16

16

by a program. When a maskable interrupt request is acknowledged,

16

19. Usage Notes

” after reset.

16

________

in the

0

to

Related parts for R5F21134DFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: