SC68C752BIBS,157 NXP Semiconductors, SC68C752BIBS,157 Datasheet - Page 29

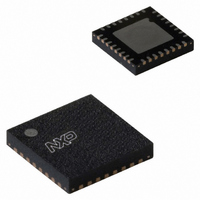

SC68C752BIBS,157

Manufacturer Part Number

SC68C752BIBS,157

Description

IC UART DUAL 32HVQFN

Manufacturer

NXP Semiconductors

Datasheet

1.SC68C752BIBS128.pdf

(48 pages)

Specifications of SC68C752BIBS,157

Number Of Channels

2, DUART

Fifo's

64 Byte

Voltage - Supply

2.5V, 3.3V, 5V

With Auto Flow Control

Yes

With False Start Bit Detection

Yes

With Modem Control

Yes

Mounting Type

Surface Mount

Package / Case

32-VFQFN Exposed Pad

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

935280969157

SC68C752BIBS

SC68C752BIBS

SC68C752BIBS

SC68C752BIBS

NXP Semiconductors

SC68C752B_4

Product data sheet

7.10 Enhanced Feature Register (EFR)

7.12 Transmission Control Register (TCR)

7.11 Divisor latches (DLL, DLM)

This 8-bit register enables or disables the enhanced features of the UART.

shows the Enhanced Feature Register bit settings.

Table 20.

These are two 8-bit registers which store the 16-bit divisor for generation of the baud clock

in the baud rate generator. DLM stores the most significant part of the divisor. DLL stores

the least significant part of the divisor.

Note that DLL and DLM can only be written to before Sleep mode is enabled, that is,

before IER[4] is set.

This 8-bit register is used to store the receive FIFO threshold levels to stop/start

transmission during hardware/software flow control.

register bit settings.

Table 21.

TCR trigger levels are available from 0 bytes to 60 bytes with a granularity of four.

Bit

7

6

5

4

3:0

Bit

7:4

3:0

Symbol

TCR[7:4]

TCR[3:0]

Symbol

EFR[7]

EFR[6]

EFR[5]

EFR[4]

EFR[3:0] Combinations of software flow control can be selected by programming these

Enhanced Feature Register bits description

Transmission Control Register bits description

Description

CTS flow control enable.

RTS flow control enable.

Special character detect.

Enhanced functions enable bit.

bits. See

Description

receive FIFO trigger level to resume transmission (0 bytes to 60 bytes).

receive FIFO trigger level to halt transmission (0 bytes to 60 bytes).

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

logic 0 = CTS flow control is disabled (normal default condition)

logic 1 = CTS flow control is enabled. Transmission will stop when a HIGH

signal is detected on the CTSn pin.

logic 0 = RTS flow control is disabled (normal default condition)

logic 1 = RTS flow control is enabled. The RTSn pin goes HIGH when the

receiver FIFO halt trigger level TCR[3:0] is reached, and goes LOW when the

receiver FIFO resume transmission trigger level TCR[7:4] is reached.

logic 0 = special character detect disabled (normal default condition)

logic 1 = special character detect enabled. Received data is compared with

Xoff2 data. If a match occurs, the received data is transferred to FIFO and

IIR[4] is set to a logic 1 to indicate a special character has been detected.

logic 0 = disables enhanced functions and writing to IER[7:4], FCR[5:4],

MCR[7:5]

logic 1 = enables the enhanced function IER[7:4], FCR[5:4], and MCR[7:5]

can be modified, that is, this bit is therefore a write enable

Rev. 04 — 20 January 2010

Table 4 “Software flow control options (EFR[3:0])” on page

Table 21

shows transmission control

SC68C752B

© NXP B.V. 2010. All rights reserved.

Table 20

9.

29 of 48