EP1SGX25CF672C7 Altera, EP1SGX25CF672C7 Datasheet - Page 199

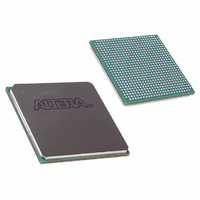

EP1SGX25CF672C7

Manufacturer Part Number

EP1SGX25CF672C7

Description

IC STRATIX GX FPGA 25KLE 672FBGA

Manufacturer

Altera

Series

Stratix® GXr

Datasheet

1.EP1SGX10CF672C7N.pdf

(272 pages)

Specifications of EP1SGX25CF672C7

Number Of Logic Elements/cells

25660

Number Of Labs/clbs

2566

Total Ram Bits

1944576

Number Of I /o

455

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

672-FBGA

Family Name

Stratix GX

Number Of Logic Blocks/elements

25660

# I/os (max)

455

Frequency (max)

4.38597GHz

Process Technology

SRAM

Operating Supply Voltage (typ)

1.5V

Logic Cells

25660

Ram Bits

1944576

Operating Supply Voltage (min)

1.425V

Operating Supply Voltage (max)

1.575V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

672

Package Type

FC-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1SGX25CF672C7

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 199 of 272

- Download datasheet (3Mb)

Stratix GX

Automated

Single Event

Upset (SEU)

Detection

Altera Corporation

February 2005

Local Update Mode

Local update mode is a simplified version of the remote update. This

feature is intended for simple systems that need to load a single

application configuration immediately upon power-up without loading

the factory configuration first. Local update designs have only one

application configuration to load, so it does not require a factory

configuration to determine which application configuration to use.

Figure 5–3

Figure 5–3. Local Update Transition Diagram

Stratix GX devices offer on-chip circuitry for automated checking of

single event upset (SEU) detection. Some applications that require the

device to operate error free at high elevations or in close proximity to

earth’s North or South Pole require periodic checks to ensure continued

data integrity. The error detection cyclic redundancy code (CRC) feature

controlled by the Device & Pin Options dialog box in the Quartus II

software uses a 32-bit CRC circuit to ensure data reliability and is one of

the best options for mitigating SEU.

nCONFIG

shows the transition diagram for local update mode.

Configuration

Error

Configuration

Configuration

or nCONFIG

Application

Power-Up

Factory

Stratix GX Device Handbook, Volume 1

Configuration

Error

Configuration & Testing

nCONFIG

5–7

Related parts for EP1SGX25CF672C7

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: