AT91RM3400-DK Atmel, AT91RM3400-DK Datasheet - Page 160

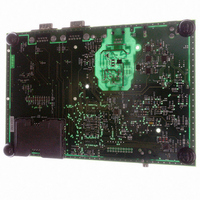

AT91RM3400-DK

Manufacturer Part Number

AT91RM3400-DK

Description

KIT DEV FOR AT91RM3400

Manufacturer

Atmel

Series

AT91SAM Smart ARMr

Type

MCUr

Datasheets

1.AT91RM3400-DK.pdf

(461 pages)

2.AT91RM3400-DK.pdf

(2 pages)

3.AT91RM3400-DK.pdf

(25 pages)

Specifications of AT91RM3400-DK

Contents

Evaluation Board, Software and Documentation

Processor To Be Evaluated

AT91RM3400

Data Bus Width

32 bit

Interface Type

RS-232, USB

For Use With/related Products

AT91RM3400

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 160 of 461

- Download datasheet (6Mb)

ST Period Interval Mode Register

Register Name: ST_PIMR

Access Type:

• PIV: Period Interval Value

Defines the value loaded in the 16-bit counter of the period interval timer. The maximum period is obtained by programming

PIV at 0x0 corresponding to 65536 slow clock cycles.

ST Watchdog Mode Register

Register Name: ST_WDMR

Access Type:

• WDV: Watchdog Counter Value

Defines the value loaded in the 16-bit counter. The maximum period is obtained by programming WDV to 0x0 correspond-

ing to 65536 x 128 slow clock cycles.

• RSTEN: Reset Enable

0 = No reset is generated when a watchdog overflow occurs.

1 = An internal reset is generated when a watchdog overflow occurs.

• EXTEN: External Signal Assertion Enable

0 = The watchdog_overflow is not tied low when a watchdog overflow occurs.

1 = The watchdog_overflow is tied low during 8 slow clock cycles when a watchdog overflow occurs.

160

31

23

15

–

–

–

–

7

AT91RM3400

Read/Write

Read/Write

30

22

14

–

–

–

–

6

29

21

13

–

–

–

–

5

28

20

12

–

–

–

–

4

WDV

WDV

PIV

PIV

27

19

11

–

–

–

–

3

26

18

10

–

–

–

–

2

EXTEN

25

17

–

–

–

9

1

1790A–ATARM–11/03

RSTEN

24

16

–

–

–

8

0

Related parts for AT91RM3400-DK

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: