AT91RM3400-DK Atmel, AT91RM3400-DK Datasheet - Page 450

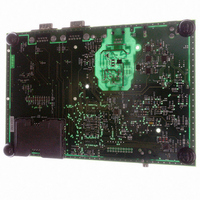

AT91RM3400-DK

Manufacturer Part Number

AT91RM3400-DK

Description

KIT DEV FOR AT91RM3400

Manufacturer

Atmel

Series

AT91SAM Smart ARMr

Type

MCUr

Datasheets

1.AT91RM3400-DK.pdf

(461 pages)

2.AT91RM3400-DK.pdf

(2 pages)

3.AT91RM3400-DK.pdf

(25 pages)

Specifications of AT91RM3400-DK

Contents

Evaluation Board, Software and Documentation

Processor To Be Evaluated

AT91RM3400

Data Bus Width

32 bit

Interface Type

RS-232, USB

For Use With/related Products

AT91RM3400

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 450 of 461

- Download datasheet (6Mb)

1790A–ATARM–11/03

Reset Controller............................................................................................. 77

Memory Controller (MC)................................................................................ 79

Peripheral Data Controller (PDC) ................................................................. 93

Overview............................................................................................................ 77

NRST Conditions .............................................................................................. 77

Reset Management ........................................................................................... 78

Recommended Features of the Reset Controller .......................................... 78

Overview............................................................................................................ 79

Block Diagram................................................................................................... 80

Functional Description..................................................................................... 81

AT91RM3400 Memory Controller (MC) User Interface .................................. 85

Overview............................................................................................................ 93

Block Diagram................................................................................................... 93

Functional Description..................................................................................... 94

Peripheral Data Controller (PDC) User Interface .......................................... 96

Sine Service ................................................................................................... 76

Bus Arbiter ..................................................................................................... 81

Address Decoder ........................................................................................... 81

Remap Command .......................................................................................... 82

Abort Status ................................................................................................... 83

Memory Protection Unit.................................................................................. 83

Misalignment Detector ................................................................................... 84

MC Remap Control Register .......................................................................... 86

MC Abort Status Register .............................................................................. 87

MC Abort Address Status Register ................................................................ 89

MC Protection Unit Area 0 to 15 Registers .................................................... 90

MC Protection Unit Peripheral........................................................................ 91

MC Protection Unit Enable Register .............................................................. 92

Configuration.................................................................................................. 94

Memory Pointers ............................................................................................ 94

Transfer Counters .......................................................................................... 94

Data Transfers ............................................................................................... 95

Priority of PDC Transfer Requests ................................................................. 95

PDC Receive Pointer Register ....................................................................... 96

PDC Receive Counter Register ..................................................................... 97

PDC Transmit Pointer Register ...................................................................... 97

PDC Transmit Counter Register .................................................................... 97

PDC Receive Next Pointer Register .............................................................. 98

PDC Receive Next Counter Register ............................................................. 98

PDC Transmit Next Pointer Register ............................................................. 98

PDC Transmit Next Counter Register ............................................................ 99

PDC Transfer Control Register ...................................................................... 99

AT91RM3400

iii

Related parts for AT91RM3400-DK

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: