AT91RM3400-DK Atmel, AT91RM3400-DK Datasheet - Page 428

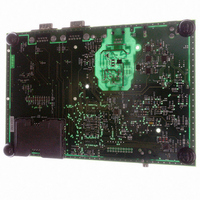

AT91RM3400-DK

Manufacturer Part Number

AT91RM3400-DK

Description

KIT DEV FOR AT91RM3400

Manufacturer

Atmel

Series

AT91SAM Smart ARMr

Type

MCUr

Datasheets

1.AT91RM3400-DK.pdf

(461 pages)

2.AT91RM3400-DK.pdf

(2 pages)

3.AT91RM3400-DK.pdf

(25 pages)

Specifications of AT91RM3400-DK

Contents

Evaluation Board, Software and Documentation

Processor To Be Evaluated

AT91RM3400

Data Bus Width

32 bit

Interface Type

RS-232, USB

For Use With/related Products

AT91RM3400

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 428 of 461

- Download datasheet (6Mb)

Please refer to chapters 8.4.5 and 9.4.5 of the Universal Serial Bus Specification, Rev. 2.0 to get more information on the

STALL handshake.

Control endpoints: during the data stage and status stage, this indicates that the microcontroller can not complete the

request.

Bulk and interrupt endpoints: notify the host that the endpoint is halted.

The host acknowledges the STALL, device firmware is notified by the STALLSENT flag.

• RX_DATA_BK1: Receive Data Bank 1 (only used by endpoints with ping-pong attributes)

This flag generates an interrupt while it is set to one.

Write (Cleared by the firmware)

0 = Notify USB device that data have been read in the FIFO’s Bank 1.

1 = No effect.

Read (Set by the USB peripheral)

0 = No data packet has been received in the FIFO's Bank 1.

1 = A data packet has been received, it has been stored in FIFO's Bank 1.

When the device firmware has polled this bit or has been interrupted by this signal, it must transfer data from the FIFO to

microcontroller memory. The number of bytes received is available in RXBYTECNT field. Bank 1 FIFO values are read

through USB_FDRx register. Once a transfer is done, the device firmware must release Bank 1 to the USB device by clear-

ing RX_DATA_BK1.

• DIR: Transfer Direction (only available for control endpoints)

Read/Write

0 = Allow Data OUT transactions in the control data stage.

1 = Enable Data IN transactions in the control data stage.

Please refer to Chapter 8.5.3 of the Universal Serial Bus Specification, Rev. 2.0 to get more information on the control data

stage.

This bit must be set before USB_CSRx/RXSETUP is cleared at the end of the setup stage. According to the request sent in

the setup data packet, the data stage is either a device to host (DIR = 1) or host to device (DIR = 0) data transfer. It is not

necessary to check this bit to reverse direction for the status stage.

• EPTYPE[2:0]: Endpoint Type

Read/Write

• DTGLE: Data Toggle

Read-only

0 = Identifies DATA0 packet.

1 = Identifies DATA1 packet.

Please refer to Chapter 8 of the Universal Serial Bus Specification, Rev. 2.0 to get more information on DATA0, DATA1

packet definitions.

428

000

001

101

010

110

011

111

AT91RM3400

Control

Isochronous OUT

Isochronous IN

Bulk OUT

Bulk IN

Interrupt OUT

Interrupt IN

1790A–ATARM–11/03

Related parts for AT91RM3400-DK

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: