FPF2025 Fairchild Semiconductor, FPF2025 Datasheet

FPF2025

Specifications of FPF2025

Related parts for FPF2025

FPF2025 Summary of contents

Page 1

... If the overcurrent condition persists beyond the 10ms Blanking Time, FPF2024 and FPF2025 pull the fault signal pin (FLAGB) low and shut-off the switch. An Auto-Restart feature turns FPF2024 and FPF2025 on again after 70ms if the ON pin is still active. The FPF2026 ...

Page 2

... PROTECTION FLAGB GND V IN UVLO ON THERMAL PROTECTION FLGAB GND ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final OUT FPF2024, FPF2026, FPF2027 ON FLAGB OUT FPF2025 ON FLAGB FPF2024, FPF2026, FPF2027 CONTROL LOGIC CURRENT LIMIT FPF2025 CONTROL LOGIC CURRENT LIMIT 2 TO LOAD TO LOAD V OUT V OUT www.fairchildsemi.com ...

Page 3

... Supply Input: Input to the power switch and the supply voltage for the IC Ground No Connection Fault Output: Active LO, open drain output for FPF2024/6/7 and CMOS output for FPF2025. FLAGB indicates an over current, supply under voltage or over temperature state ON/OFF Control Input, Active High for FPF2024/6/7 and Active LO for FPF2025 ...

Page 4

... 5. GND SWOFF ON IN OUT V = 5.5V 1mA IN SINK V = 1.8V 1mA IN SINK V = 5.5V 1mA, FPF2025 IN SOURCE V = 1.6V 1mA, FPF2025 IN SOURCE V = 5.5V, Switch on, IN FPF2024, FPF2026, FPF2027 3.3V 3.0V,T = 25°C LIM IN OUT A Shutdown Threshold T increasing J Return from Shutdown Hysteresis UVLO V Increasing 500Ω 0.1µ ...

Page 5

... Temperature ( Figure 1. Shutdown Current vs.Temperature 1200 1100 1000 V 900 800 700 600 -50 -25 0 Temperature ( Figure 3. Quiescent Current vs. Temperature 350 300 250 200 150 Figure 5. R DS(ON) ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final 100 - 10.4 10 1.8V IN 9.8 9.6 9.4 9 ...

Page 6

... V vs Temperature 2V/DIV V ON 2V/DIV I LOAD 10mA/DIV V OUT 2V/DIV 100us/DIV Figure 11. FPF2024 T Note3: V signal forces the device to go into overcurrent condition by loading a 7.5Ω. DRV ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final. B 160 o -40 C 159 158 o - 157 o C 156 C 155 154 153 ...

Page 7

... 2V/DIV I LOAD 100mA/DIV V OUT 2V/DIV Figure 17. FPF2024 Current Limit Response (Input and enable pin are tied together and V is shorted to GND) OUT ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final. B =3. 2V/DIV =0.1uF V ON 2V/DIV RESTART I LOAD 100mA/DIV V OUT ...

Page 8

... Figure 19. FPF2027 Startup FLAGB Blanking Time ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final 2V/DIV V =3. =10uF IN C =10uF OUT FLAGB R =5Ω L 2V/DIV I LOAD 100mA/DIV V OUT 2V/DIV Figure 20. FPF2025 =3.3V IN Device =10uF IN C =0.1uF OUT R =7.5Ω L 20ms/DIV and T BLANK RESTART (Active LO Device) www.fairchildsemi.com ...

Page 9

... Blanking Time of 10ms (typ) from triggering the fault signal (FLAGB) output. If the over-current condition persists beyond the Blanking Time, the FPF2024 and FPF2025 pull the FLAGB pin low and shut the switch off. If the ON pin is kept active, an Auto-Restart feature releases the FLAGB pin and turns the switch on again after 70ms ...

Page 10

... If the temperature of the die drops below the threshold temperature, the switch automatically turns- on again, To avoid unwanted thermal oscillations, a 10°C (typ) thermal hysteresis is implemented between thermal shutdown entry and exit temperatures. ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final www.fairchildsemi.com ...

Page 11

... I FAULT END 70ms AUTO- RESTART 70ms Figure 21. Representative State Diagram of FPF2024/5 ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final. B Notes: All States return to OFF when ON is removed. Typical timing values are shown . Key: I=Load Switch current, V=Input Voltage, T= Die Temperature I FAULT ...

Page 12

... STARTUP & BLANKING (Full-feature for 10ms FAULT Figure 22. Representative State Diagram of FPF2026 ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final. B Notes: All States return to OFF when ON is removed. Typical timing values are shown . Key: I=Load Switch current, V=Input Voltage, T=Die Temperature I FAULT SLEEP ...

Page 13

... State Diagram for the part options with no Blanking (FPF2027 & ull-feature for 10m Figure 23. Representative State Diagram of FPF2027 ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final. B Notes: All States return to OFF w hen ON is rem oved. T ypical tim ing values are show n . Key : I= Load Switch current, V=Input Voltage perature EEP ( onitor SW ...

Page 14

... IN output voltage and simulates an over-current condition. The R2 resistor is connected between FLAGB pin and input voltage as pull-up resistor for FPF2024, FPF2026 and FPF2027 devices. The FPF2025 does not require a pull-up resistor due to its , and the Over CMOS output structure. RSTRT The thermal performance of the board is improved using the techniques recommended in the layout recommendations section of datasheet ...

Page 15

... Figure 25. Top Layer Figure 26. Bottom Layer Figure 27. SST ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final. B Figure 28. TOP, SST and SMT 15 www.fairchildsemi.com ...

Page 16

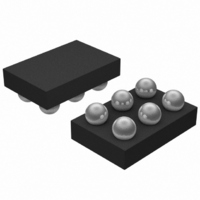

... Dimensional Outline and Pad Layout Product FPF2024/5/6/7 1.500+/- 0.030 ©2008 Fairchild Semiconductor Corporation FPF2024/5/6/7 Final 1.000 +/-0.030 0.240 0.240 www.fairchildsemi.com ...

Page 17

... TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidianries, and is not intended exhaustive list of all such trademarks. Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT™ CTL™ Current Transfer Logic™ ...