EP2SGX130GF1508I4 Altera, EP2SGX130GF1508I4 Datasheet - Page 98

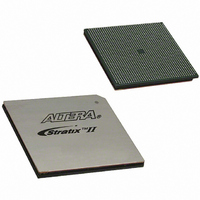

EP2SGX130GF1508I4

Manufacturer Part Number

EP2SGX130GF1508I4

Description

IC STRATIX II GX 130K 1508-FBGA

Manufacturer

Altera

Series

Stratix® II GXr

Datasheet

1.EP2SGX30DF780C5.pdf

(316 pages)

Specifications of EP2SGX130GF1508I4

Number Of Logic Elements/cells

132540

Number Of Labs/clbs

6627

Total Ram Bits

6747840

Number Of I /o

734

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

1508-FBGA

Family Name

Stratix II GX

Number Of Logic Blocks/elements

132540

# I/os (max)

734

Frequency (max)

732.1MHz

Process Technology

SRAM

Operating Supply Voltage (typ)

1.2V

Logic Cells

132540

Ram Bits

6747840

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

1508

Package Type

FC-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-2174

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2SGX130GF1508I4N

Manufacturer:

Sunon

Quantity:

1 000

Part Number:

EP2SGX130GF1508I4N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 98 of 316

- Download datasheet (2Mb)

PLLs and Clock Networks

Figure 2–61. Global Clocking

2–90

Stratix II GX Device Handbook, Volume 1

CLK[3..0]

generated global clocks and asynchronous clears, clock enables, or other

control signals with large fanout.

pins driving global clock networks.

Regional Clock Network

There are eight regional clock networks (RCLK[7..0]) in each quadrant

of the Stratix II GX device that are driven by the dedicated

CLK[15..12]and CLK[7..0] input pins, by PLL outputs, or by internal

logic. The regional clock networks provide the lowest clock delay and

skew for logic contained in a single quadrant. The CLK pins

symmetrically drive the RCLK networks in a particular quadrant, as

shown in

Figure

Global Clock [15..0]

2–62.

CLK[7..4]

CLK[15..12]

Figure 2–61

Global Clock [15..0]

shows the 12 dedicated CLK

Altera Corporation

October 2007

Related parts for EP2SGX130GF1508I4

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: