CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 55

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

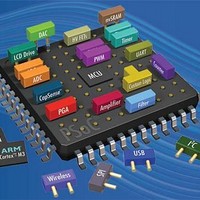

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample

conversion on a trigger. In this mode, the ADC stays in standby

state waiting for the SoC signal to be asserted. When SoC is

signaled the ADC performs four successive conversions. The

first three conversions prime the decimator. The ADC result is

valid and available after the fourth conversion, at which time the

EoC signal is generated. To detect the end of conversion, the

system may poll a control register for status or configure the

external EoC signal to generate an interrupt or invoke a DMA

request. When the transfer is done the ADC reenters the standby

state where it stays until another SoC event.

8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive

samples of a single input signal. Multiplexing multiple inputs

should not be done with this mode. There is a latency of three

conversion times before the first conversion result is available.

This is the time required to prime the decimator. After the first

result, successive conversions are available at the selected

sample rate.

8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the

ADC is reset between samples. This mode is useful when the

input is switched between multiple signals. The decimator is

re-primed between each sample so that previous samples do not

affect the current conversion. Upon completion of a sample, the

next sample is automatically initiated. The results can be

transferred using either firmware polling, interrupt, or DMA.

8.2.2.4 Multi Sample (Turbo)

The multi sample (turbo) mode operates identical to the

Multi-sample mode for resolutions of 8 to 16 bits. For resolutions

of 17 to 20 bits, the performance is about four times faster than

the multi sample mode, because the ADC is only reset once at

the end of conversion.

More information on output formats is provided in the Technical

Reference Manual.

Document Number: 001-11729 Rev. *R

8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital

clock or UDB output can be used to drive this input. It can be

used when the sampling period must be longer than the ADC

conversion time or when the ADC must be synchronized to other

hardware. This signal is optional and does not need to be

connected if ADC is running in a continuous mode.

8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion.

This signal may be used to trigger either an interrupt or DMA

request.

8.3 Comparators

The CY8C38 family of devices contains four comparators in a

device. Comparators have these features:

8.3.1 Input and Output Interface

The positive and negative inputs to the comparators come from

the analog global buses, the analog mux line, the analog local

bus and precision reference through multiplexers. The output

from each comparator could be routed to any of the two input

LUTs. The output of that LUT is routed to the UDB DSI.

Input offset factory trimmed to less than 5 mV

Rail-to-rail common mode input range (V

Speed and power can be traded off by using one of three

modes: fast, slow, or ultra low-power

Comparator outputs can be routed to lookup tables to perform

simple logic functions and then can also be routed to digital

blocks

The positive input of the comparators may be optionally passed

through a low pass filter. Two filters are provided

Comparator inputs can be connections to GPIO, DAC outputs

and SC block outputs

PSoC

®

3: CY8C38 Family

SSA

Data Sheet

to V

Page 55 of 129

DDA

)

[+] Feedback