CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 33

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

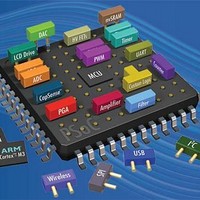

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High

Voltage Interrupt

6.3.1.2 Other Reset Sources

Document Number: 001-11729 Rev. *R

Note

Interrupt Supply

14. GPIOs with opamp outputs are not recommended for use with CapSense.

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog

high voltage interrupt

Interrupt circuits are available to detect when Vdda and Vddd

go outside a voltage range. For AHVI, Vdda is compared to a

fixed trip level. For ALVI and DLVI, Vdda and Vddd are

compared to trip levels that are programmable, as listed in

Table

a device reset instead of an interrupt.

The monitors are disabled until after IPOR. During sleep mode

these circuits are periodically activated (buzzed). If an interrupt

occurs during buzzing then the system first enters its wakeup

sequence. The interrupt is then recognized and may be

serviced.

XRES – External reset

PSoC 3 has either a single GPIO pin that is configured as an

external reset or a dedicated XRES pin. Either the dedicated

XRES pin or the GPIO pin, if configured, holds the part in reset

while held active (low). The response to an XRES is the same

as to an IPOR reset.

The external reset is active low. It includes an internal pull-up

resistor. XRES is active during sleep and hibernate modes.

SRES – Software reset

A reset can be commanded under program control by setting

a bit in the software reset register. This is done either directly

by the program or indirectly by DMA access. The response to

a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

WRES – Watchdog timer reset

The watchdog reset detects when the software program is no

longer being executed correctly. To indicate to the watchdog

timer that it is running correctly, the program must periodically

reset the timer. If the timer is not reset before a user-specified

amount of time, then a reset is generated.

Note IPOR disables the watchdog function. The program must

enable the watchdog function at an appropriate point in the

code by setting a register bit. When this bit is set, it cannot be

cleared again except by an IPOR power on reset event.

AHVI

DLVI

ALVI

6-5. ALVI and DLVI can also be configured to generate

V

V

V

DDD

DDA

DDA

1.71 V–5.5 V 1.70 V–5.45 V in

1.71 V–5.5 V 1.70 V–5.45 V in

1.71 V–5.5 V 5.75 V

Voltage

Normal

Range

250 mV

increments

250 mV

increments

Available Trip

Settings

Accuracy

±2%

±2%

±2%

6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and

digital I/O capability. All I/Os have a large number of drive modes,

which are set at POR. PSoC also provides up to four individual

I/O voltage domains through the Vddio pins.

There are two types of I/O pins on every device; those with USB

provide a third type. Both GPIO and SIO provide similar digital

functionality. The primary differences are their analog capability

and drive strength. Devices that include USB also provide two

USBIO pins that support specific USB functionality as well as

limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for

both the CPU and digital peripherals. In addition, all I/O pins can

generate an interrupt. The flexible and advanced capabilities of

the PSoC I/O, combined with any signal to any pin routability,

greatly simplify circuit design and board layout. All GPIO pins can

be used for analog input, CapSense

while SIO pins are used for voltages in excess of V

programmable output voltages.

Features supported by both GPIO and SIO:

Additional features only provided on the GPIO pins:

Additional features only provided on SIO pins:

USBIO features:

User programmable port reset state

Separate I/O supplies and voltages for up to four groups of I/O

Digital peripherals use DSI to connect the pins

Input or output or both for CPU and DMA

Eight drive modes

Every pin can be an interrupt source configured as rising

edge, falling edge or both edges. If required, level sensitive

interrupts are supported through the DSI

Dedicated port interrupt vector for each port

Slew rate controlled digital output drive mode

Access port control and configuration registers on either port

basis or pin basis

Separate port read (PS) and write (DR) data registers to avoid

read modify write errors

Special functionality on a pin by pin basis

LCD segment drive on LCD equipped devices

CapSense

Analog input and output capability

Continuous 100 µA clamp current capability

Standard drive strength down to 1.7 V

Higher drive strength than GPIO

Hot swap capability (5 V tolerance at any operating V

Programmable and regulated high input and output drive

levels down to 1.2 V

No analog input, CapSense, or LCD capability

Over voltage tolerance up to 5.5 V

SIO can act as a general purpose analog comparator

Full speed USB 2.0 compliant I/O

Highest drive strength for general purpose use

Input, output, or both for CPU and DMA

Input, output, or both for digital peripherals

Digital output (CMOS) drive mode

Each pin can be an interrupt source configured as rising

edge, falling edge, or both edges

[14]

PSoC

®

3: CY8C38 Family

[14]

, and LCD segment drive,

Data Sheet

Page 33 of 129

DDA

and for

DD

)

[+] Feedback