CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet

CY8C3866AXI-040

Specifications of CY8C3866AXI-040

Available stocks

Related parts for CY8C3866AXI-040

CY8C3866AXI-040 Summary of contents

Page 1

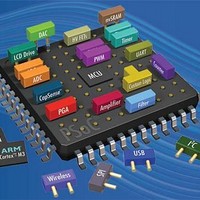

... AHB – AMBA (advanced microcontroller bus architecture) high-performance bus, an ARM data transfer bus 2. This feature on select devices only. See Ordering Information 3. GPIOs with opamp outputs are not recommended for use with CapSense. Cypress Semiconductor Corporation Document Number: 001-11729 Rev. *R Programmable System-on-Chip (PSoC ® ...

Page 2

Contents 1. Architectural Overview .................................................... 3 2. Pinouts .............................................................................. 5 3. Pin Descriptions ............................................................. 10 4. CPU .................................................................................. 11 4.1 8051 CPU ................................................................ 11 4.2 Addressing Modes ................................................... 11 4.3 Instruction Set ......................................................... 11 4.4 DMA and PHUB ...................................................... 15 ...

Page 3

Architectural Overview Introducing the CY8C38 family of ultra low-power, flash Programmable System-on-Chip (PSoC PSoC 3 and 32-bit PSoC 5 platform. The CY8C38 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of ...

Page 4

For more details on the peripherals see the Peripherals” section on page 40 of this data sheet. For information on UDBs, DSI, and other digital blocks, see the “Digital Subsystem” section on page 39 of this data sheet. PSoC’s analog ...

Page 5

It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in real-time clock (RTC) applications. The clocks, together with programmable clock dividers, provide ...

Page 6

P2[7] (GPIO, TMS, SWDIO) P1[0] (GPIO, TCK, SWDCK) P1[1] (GPIO, Configurable XRES) P1[2] (GPIO, TDO, SWV) P1[3] (GPIO, TDI) P1[4] (GPIO, nTRST) P1[5] Notes 7. Pins are Do Not Use (DNU) on devices without USB. The pin must be ...

Page 7

P2[6] (GPIO) P2[7] (I2C0: SCL, SIO) P12[4] (I2C0: SDA, SIO) P12[5] Vboost XRES (TMS, SWDIO, GPIO) P1[0] (TCK, SWDCK, GPIO) P1[1] (configurable XRES, GPIO) P1[2] (TDO, SWV, GPIO) P1[3] (TDI, GPIO) P1[4] (nTRST, GPIO) P1[5] Vddio1 Notes 9. The ...

Page 8

P2[5] (GPIO) P2[6] (GPIO) P2[7] (I2C0: SCL, SIO) P12[4] (I2C0: SDA, SIO) P12[5] (GPIO) P6[4] (GPIO) P6[5] (GPIO) P6[6] (GPIO) P6[7] Vssb Ind Vboost Vbat Vssd XRES (GPIO) P5[0] (GPIO) P5[1] (GPIO) P5[2] (GPIO) P5[3] (TMS, SWDIO, GPIO) P1[0] ...

Page 9

Figure 2-5. Example Schematic for 100-pin TQFP Part with Power Connections Vddd C6 0.1 uF Vssd 1 P2[5] 2 P2[6] 3 P2[7] 4 P12[4], SIO 5 P12[5], SIO 6 P6[4] 7 P6[5] 8 P6[6] 9 P6[7] 10 Vssb 11 Ind ...

Page 10

Figure 2-6. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance Vssd Plane 3. Pin Descriptions IDAC0, IDAC1, IDAC2, IDAC3 Low resistance output pin for high current DACs (IDAC). OpAmp0out, OpAmp1out, OpAmp2out, OpAmp3out High current output of uncommitted ...

Page 11

TMS JTAG test mode select programming and debug port connection. USBIO, D+ Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin powered from V DDD Vddio. Pins are Do Not ...

Page 12

Instruction Set Summary 4.3.1.1 Arithmetic Instructions Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions. Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations. instructions. Table 4-1. Arithmetic Instructions Mnemonic ADD A,Rn ...

Page 13

Table 4-2. Logical Instructions (continued) Mnemonic ANL Direct, #data AND immediate data to direct byte ORL A,Rn OR register to accumulator ORL A,Direct OR direct byte to accumulator ORL A,@Ri OR indirect RAM to accumulator ORL A,#data OR immediate data ...

Page 14

Table 4-3. Data Transfer Instructions (continued) Mnemonic MOV Direct, Direct Move direct byte to direct byte MOV Direct, @Ri Move indirect RAM to direct byte MOV Direct, #data Move immediate data to direct byte MOV @Ri, A Move accumulator to ...

Page 15

Program Branching Instructions The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. shows the list of jump instructions. Table 4-5. Jump Instructions Mnemonic ACALL addr11 Absolute subroutine call LCALL ...

Page 16

DMA Features 24 DMA channels Each channel has one or more transaction descriptors (TD) to configure channel behavior 128 total TDs can be defined TDs can be dynamically updated Eight levels of priority per channel Any digitally ...

Page 17

Auto Repeat DMA Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself. 4.4.4.3 Ping Pong DMA ...

Page 18

CLK Arrival of new Interrupt INT_INPUT Pend bit is set on next system clock active edge PEND Interrupt is posted to ascertain the priority POST Interrupt request sent to core for processing IRQ ACTIVE_INT_NUM NA (#10) ...

Page 19

Interrupts form Fixed function blocks, DMA and UDBs Interrupts from UDBs Interrupts from Fixed Function Blocks Interrupt Interrupts 0 to routing logic 30 from DMA to select 31 sources When an interrupt is pending, ...

Page 20

Table 4-8. Interrupt Vector Table # Fixed Function DMA 0 LVD phub_termout0[0] 1 ECC phub_termout0[1] 2 Reserved phub_termout0[2] 3 Sleep (Pwr Mgr) phub_termout0[3] 4 PICU[0] phub_termout0[4] 5 PICU[1] phub_termout0[5] 6 PICU[2] phub_termout0[6] 7 PICU[3] phub_termout0[7] 8 PICU[4] phub_termout0[8] 9 PICU[5] ...

Page 21

Memory 5.1 Static RAM CY8C38 SRAM is used for temporary data storage SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 24. Simultaneous access ...

Page 22

Nonvolatile Latches (NVLs) PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2. Table 5-2. Device Configuration NVL Register Map Register Address ...

Page 23

External Memory Interface CY8C38 provides an EMIF for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory ...

Page 24

Memory Map The CY8C38 8051 memory map is very similar to the MCS-51 memory map. 5.7.1 Code Space The CY8C38 8051 code space is 64 KB. Only main flash exists in this space. See the Flash Program Memory 5.7.2 ...

Page 25

INC DPTR MOV DPTR, #data16 The extended data pointer SFRs, DPX0, DPX1, MXAX, and P2AX, hold the most significant parts of memory addresses during access to the xdata space. These SFRs are used only with the MOVX instructions. During a ...

Page 26

System Integration 6.1 Clocking System The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate MHz ...

Page 27

MHz 4-25 MHz IMO ECO 12-48 MHz Doubler Digital Clock Divider 16 bit Digital Clock Divider 16 bit 7 Digital Clock Divider 16 bit Digital Clock Divider 16 bit 6.1.1 Internal Oscillators 6.1.1.1 Internal Main Oscillator In most designs ...

Page 28

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal. 6.1.2 External Oscillators 6.1.2.1 MHz External Crystal Oscillator ...

Page 29

Power System The power system consists of separate analog, digital, and I/O supply pins, labeled Vdda, Vddd, and Vddiox, respectively. It also includes two internal 1.8-V regulators that provide the digital (Vccd) and analog (Vcca) supplies for the internal ...

Page 30

Power Modes PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing ...

Page 31

Figure 6-5. Power Mode Transitions Active Manual Sleep Hibernate Buzz Alternate Active 6.2.1.1 Active Mode Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled ...

Page 32

In standby mode, most boost functions are disabled, thus reducing power consumption of the boost circuit. The converter can be configured to provide low-power, low-current regulation in the standby mode. The external 32-kHz crystal can be used to generate ...

Page 33

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt Interrupt circuits are available to detect when Vdda and Vddd go outside a voltage range. For AHVI, Vdda is compared to a fixed trip level. For ALVI and ...

Page 34

Digital Input Path PRT[x]CTL PRT[x]DBL_SYNC_IN PRT[x]PS Digital System Input PICU[x]INTTYPE[y] PICU[x]INTSTAT Pin Interrupt Signal PICU[x]INTSTAT Digital Output Path PRT[x]SLW PRT[x]SYNC_OUT PRT[x]DR Digital System Output PRT[x]BYP PRT[x]DM2 PRT[x]DM1 PRT[x]DM0 Bidirectional Control PRT[x]BIE Analog Capsense Global Control CAPS[x]CFG1 PRT[x]AG Analog Global Enable ...

Page 35

Digital Input Path PRT[x]SIO_HYST_EN PRT[x]SIO_DIFF Reference Level PRT[x]DBL_SYNC_IN PRT[x]PS Digital System Input PICU[x]INTTYPE[y] PICU[x]INTSTAT Pin Interrupt Signal PICU[x]INTSTAT Digital Output Path Reference Level PRT[x]SIO_CFG PRT[x]SLW PRT[x]SYNC_OUT PRT[x]DR Digital System Output PRT[x]BYP PRT[x]DM2 PRT[x]DM1 PRT[x]DM0 Bidirectional Control PRT[x]BIE Digital Input Path ...

Page 36

Drive Modes Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. drive modes. Table 6-6 shows the I/O pin’s drive ...

Page 37

High impedance analog The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O’s digital input buffer due to a floating voltage. This state is recommended for ...

Page 38

Analog Connections These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the Vddio supply voltage to which the GPIO belongs. ...

Page 39

Over Voltage Tolerance All I/O pins provide an over voltage tolerance feature at any operating There are no current limitations for the SIO pins as they present a high impedance load to the external circuit where ...

Page 40

Example Peripherals The flexibility of the CY8C38 family’s UDBs and analog blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC ...

Page 41

Component Catalog Figure 7-3. Component Catalog Document Number: 001-11729 Rev. *R Figure 7-2. PSoC Creator Framework The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device populated with ...

Page 42

Software Development Figure 7-4. Code Editor Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools. Project build control leverages ...

Page 43

The main component blocks of the UDB are: PLD blocks – There are two small PLDs per UDB. These blocks take inputs from the routing array and form registered or combinational sum-of-products logic. PLDs are used to implement state machines, ...

Page 44

Datapath Module The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators ...

Page 45

Independent of the ALU operation, these functions are available: Shift left Shift right Nibble swap Bitwise OR mask 7.2.2.3 Conditionals Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers ...

Page 46

Clock Generation Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component ...

Page 47

Figure 7-13. Digital System Interconnect Timer Interrupt DMA CAN I2C Counters Controller Controller Digital System Routing I/F UDB ARRAY Digital System Routing I/F Global IO Port SC/CT EMIF Del-Sig Clocks Pins Blocks Interrupt and DMA routing is very flexible in ...

Page 48

CAN The CAN peripheral is a fully functional controller area network (CAN) supporting communication baud rates Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ...

Page 49

Tx Buffer Status TxReq Pending TxInterrupt Request (if enabled) Acceptance Code 0 Rx Buffer RxMessage0 Status RxMessage RxMessage1 Acceptance Code 1 Available RxMessage14 Acceptance Code 14 RxInterrupt RxMessage15 Acceptance Code 15 Request (if enabled) 7.6 USB PSoC includes a dedicated ...

Page 50

Timers, Counters, and PWMs The timer/counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been ...

Page 51

Digital Filter Block Some devices in the CY8C38 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one ...

Page 52

DAC A DAC GPIO G Port The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and ...

Page 53

ExVrefL ExVrefL1 opamp0 opamp2 swinp GPIO swfol swfol P0[4] swinn GPIO P0[5] GPIO * i0 abuf_vref_int P0[6] (1.024V) GPIO * i2 P0[7] cmp0_vref (1.024V) GPIO cmp_muxvn[1:0] P4[2] vref_cmp1 cmp1_vref (0.256V) GPIO bg_vda_res_en Vdda Vdda/2 ...

Page 54

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C38, four in the left half (abusl [0:3]) and four in the ...

Page 55

Single Sample In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs ...

Page 56

From Analog Routing From Analog Routing 8.3.2 LUT The CY8C38 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. ...

Page 57

Figure 8-7. Opamp GPIO Analog Global Bus Opamp Analog Global Bus VREF Analog Internal Bus Analog Switch = GPIO The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or ...

Page 58

Table 8-3. Bandwidth Gain Bandwidth 1 6.0 MHz 24 340 kHz 48 220 kHz 50 215 kHz Figure 8-9. PGA Resistor Settings ref 980 k ...

Page 59

Figure 8-11. LCD System LCD Global DAC Clock UDB LCD Driver Block Display DMA RAM PHUB 8.6.1 LCD Segment Pin Driver Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC ...

Page 60

Reference Source 8.9.1 Current DAC The current DAC (IDAC) can be configured for the ranges µ 256 µA, and 0 to 2.048 mA. The IDAC can be configured to source or sink current. 8.9.2 Voltage ...

Page 61

Down Mixer The SC/CT block can be used as a mixer to down convert an input signal. This circuit is a high bandwidth passive sample network that can sample input signals MHz. This sampled value is ...

Page 62

Debug Features Using the JTAG or SWD interface, the CY8C38 supports the following debug features: Halt and single-step the CPU View and change CPU and peripheral registers, and RAM addresses Eight program address breakpoints One memory access breakpoint—break on ...

Page 63

Development Support The CY8C38 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more. 10.1 Documentation A suite of documentation, supports the CY8C38 family ...

Page 64

Electrical Specifications Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. The unique flexibility of the PSoC UDBs and analog blocks enable many functions to be implemented in PSoC Creator components, ...

Page 65

Device Level Specifications Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.2.1 Device Level Specifications Table 11-2. DC Specifications Parameter Description V Analog supply voltage and input to analog DDA ...

Page 66

Table 11-2. DC Specifications (continued) Parameter Description [22] Sleep Mode CPU = OFF RTC = ON (= ECO32K ON, in low-power mode) Sleep timer = ON (= ILO kHz) WDT = OFF Wake = ...

Page 67

Figure 11-1. Active Mode Current vs F Temperature = 25 °C Figure 11-3. Active Mode Current MHz CPU Document Number: 001-11729 Rev 3.3 V, Figure 11-2. Active Mode Current vs Temperature ...

Page 68

Table 11-3. AC Specifications Parameter Description F CPU frequency CPU F Bus frequency BUSCLK Svdd V ramp rate DD T Time from IO_INIT DDD DDA ≥ IPOR to I/O ports set to their reset states T ...

Page 69

Power Regulators Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.3.1 Digital Core Regulator Table 11-4. Digital Core Regulator DC Specifications Parameter Description V Input voltage DDD V Output voltage ...

Page 70

Inductive Boost Regulator. Table 11-6. Inductive Boost Regulator DC Specifications Unless otherwise specified, operating conditions are µF || 0.1 µF BOOST Parameter Description V Input voltage BAT Includes startup [25, 26] I Load current OUT ...

Page 71

Table 11-7. Inductive Boost Regulator AC Specifications Unless otherwise specified, operating conditions are µF || 0.1 µF. BOOST Parameter Description V Ripple voltage RIPPLE (peak-to-peak) F Switching frequency SW Table 11-8. Recommended External Components for Boost ...

Page 72

Figure 11-10. Efficiency vs I OUT 3.3 V BAT OUT Figure 11-12. Efficiency vs Switching Frequency OUT BAT OUT Document Number: 001-11729 ...

Page 73

Inputs and Outputs Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. Unless otherwise specified, all charts and graphs show typical values. 11.1.1 GPIO Table 11-9. GPIO DC Specifications Parameter Description ...

Page 74

Table 11-10. GPIO AC Specifications Parameter Description TriseF Rise time in Fast Strong Mode TfallF Fall time in Fast Strong Mode TriseS Rise time in Slow Strong Mode TfallS Fall time in Slow Strong Mode GPIO output operating frequency 2.7 ...

Page 75

SIO Table 11-11. SIO DC Specifications Parameter Description Vinmax Maximum input voltage Vinref Input voltage reference (Differential input mode) Output voltage reference (Regulated output mode) Voutref Input voltage high threshold GPIO mode V IH [32] Differential input mode Input ...

Page 76

Figure 11-17. SIO Output HighVoltage and Current, Unregulated Mode Figure 11-19. SIO Output High Voltage and Current, Regulat- ed Mode Table 11-12. SIO AC Specifications Parameter Description TriseF Rise time in fast strong mode [34] (90/10%) TfallF Fall time in ...

Page 77

Table 11-12. SIO AC Specifications (continued) Parameter Description SIO output operating frequency 2.7 V < V < 5.5 V, Unregulated DDIO output (GPIO) mode, fast strong drive mode 1.71 V < V < 2.7 V, DDIO Unregulated output (GPIO) mode, ...

Page 78

USBIO For operation in GPIO mode, the standard range for V Table 11-13. USBIO DC Specifications Parameter Description Rusbi USB D+ pull-up resistance Rusba USB D+ pull-up resistance Vohusb Static output high Volusb Static output low Vihgpio Input voltage ...

Page 79

Table 11-14. USBIO AC Specifications Parameter Description Tdrate Full-speed data rate average bit rate Tjr1 Receiver data jitter tolerance to next transition Tjr2 Receiver data jitter tolerance to pair transition Tdj1 Driver differential jitter to next transition Tdj2 Driver differential ...

Page 80

XRES Table 11-16. XRES DC Specifications Parameter Description V Input voltage high threshold IH V Input voltage low threshold IL Rpullup Pull-up resistor [35] C Input capacitance IN V Input voltage hysteresis H [35] (Schmitt-Trigger) Idiode Current through protection ...

Page 81

Figure 11-25. Opamp Voffset Histogram, 3388 samples/847 parts, 25 °C, Vdda = 5 V Figure 11-27. Opamp Voffset vs Vcommon and Vdda, 25 °C Figure 11-29. Opamp Operating Current vs Vdda and Power Mode Document Number: 001-11729 Rev. *R ® ...

Page 82

Table 11-19. Opamp AC Specifications Parameter Description GBW Gain-bandwidth product SR Slew rate, 20% - 80% e Input noise density n Figure 11-30. Opamp Noise vs Frequency, Power Mode = High, Vdda = 5V Figure 11-32. Opamp Step Response, ...

Page 83

Delta-sigma ADC Unless otherwise specified, operating conditions are: Operation in continuous sample mode fclk = 3.072 MHz for resolution = bits; fclk = 6.144 MHz for resolution = bits Reference = 1.024 V ...

Page 84

Table 11-20. 20-bit Delta-sigma ADC DC Specifications (continued) Parameter Description ADC external reference input voltage, see Vextref also internal reference in Voltage Reference on page 87 Current Consumption I Current consumption, 20 bit DD_20 I Current consumption, 16 bit DD_16 ...

Page 85

Table 11-22. Delta-sigma ADC Sample Rates, Range = ±1.024 V Continuous Resolution, Bits Min Max 8 8000 384000 9 6400 307200 10 5566 267130 11 4741 227555 12 4000 192000 13 3283 157538 14 2783 133565 15 2371 113777 16 ...

Page 86

Table 11-23. Delta-sigma ADC RMS Noise in Counts vs. Input Range and Sample Rate, 16-bit, Internal Reference, Single Ended Sample rate, sps 0 to VREF 2000 1.21 3000 1.28 6000 1.36 12000 1.44 24000 1.67 48000 1.91 Table 11-24. Delta-sigma ...

Page 87

Figure 11-37. Delta-sigma ADC DNL vs Output Code, 16-bit, 48 ksps, 25 ° 3.3 V DDA 11.2.3 Voltage Reference Table 11-27. Voltage Reference Specifications See also ADC external reference specifications in Section 11.2.2. Parameter Description V Precision reference ...

Page 88

Table 11-29. Comparator DC Specifications (continued) Parameter Description V Input common mode voltage ICM CMRR Common mode rejection ratio I High current mode/fast mode CMP Low current mode/slow mode [42] Ultra low-power mode Table 11-30. Comparator AC Specifications Parameter Description ...

Page 89

Table 11-31. IDAC DC Specifications (continued) Parameter Description INL Integral nonlinearity DNL Differential nonlinearity Vcompliance Dropout voltage, source or sink mode I Operating current, code = 0 DD Document Number: 001-11729 Rev. *R PSoC Conditions Min Sink mode, range = ...

Page 90

Figure 11-39. IDAC INL vs Input Code, Range = 255 µA, Source Mode Figure 11-41. IDAC DNL vs Input Code, Range = 255 µA, Source Mode Figure 11-43. IDAC INL vs Temperature, Range = 255 µA, Fast Mode Document Number: ...

Page 91

Figure 11-45. IDAC Full Scale Error vs Temperature, Range = 255 µA, Source Mode Figure 11-47. IDAC Operating Current vs Temperature, Range = 255 µA, Code = 0, Source Mode Document Number: 001-11729 Rev. *R ® PSoC 3: CY8C38 Family ...

Page 92

Table 11-32. IDAC AC Specifications Parameter Description F Update rate DAC T Settling time to 0.5 LSB SETTLE Figure 11-49. IDAC Step Response, Codes 0x40 - 0xC0, 255 µA Mode, Source Mode, Fast Mode, Vdda = 5 V Figure 11-51. ...

Page 93

Voltage Digital to Analog Converter (VDAC) See the VDAC component data sheet in PSoC Creator for full electrical specifications and APIs. Unless otherwise specified, all charts and graphs show typical values. Table 11-33. VDAC DC Specifications Parameter Description Resolution ...

Page 94

Figure 11-54. VDAC INL vs Temperature Mode Figure 11-56. VDAC Full Scale Error vs Temperature Mode Figure 11-58. VDAC Operating Current vs Temperature, 1V Mode, Slow Mode Document Number: 001-11729 Rev. *R ® PSoC 3: CY8C38 ...

Page 95

Table 11-34. VDAC AC Specifications Parameter Description F Update rate DAC TsettleP Settling time to 0.1%, step 25% to 75% TsettleN Settling time to 0.1%, step 75% to 25% Figure 11-60. VDAC Step Response, Codes 0x40 - 0xC0 ...

Page 96

Mixer The mixer is created using a SC/CT analog block; see the Mixer component data sheet in PSoC Creator for full electrical specifications and APIs. Table 11-35. Mixer DC Specifications Parameter Description V Input offset voltage OS Quiescent current ...

Page 97

Programmable Gain Amplifier The PGA is created using a SC/CT analog block; see the PGA component data sheet in PSoC Creator for full electrical specifications and APIs. Unless otherwise specified, operating conditions are: Operating temperature = 25 °C for ...

Page 98

Table 11-40. PGA AC Specifications Parameter Description BW1 –3 dB bandwidth SR1 Slew rate e Input noise density n Figure 11-64. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High 11.2.11 Temperature Sensor Table 11-41. Temperature Sensor Specifications ...

Page 99

Table 11-42. LCD Direct Drive DC Specifications (continued) Parameter Description Long term segment offset I Output drive current per segment OUT driver) Table 11-43. LCD Direct Drive AC Specifications Parameter Description f LCD frame rate LCD 11.3 Digital Peripherals Specifications ...

Page 100

Counter The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component data sheet in PSoC Creator. Table 11-46. Counter DC Specifications Parameter Description Block ...

Page 101

Table 11-50. Fixed Specifications Parameter Description Block current consumption – – 2 Table 11-51. Fixed Specifications Parameter Description Bit rate [44] 11.3.5 Controller Area Network Table 11-52. CAN DC ...

Page 102

USB Table 11-56. USB DC Specifications Parameter Description V Device supply for USB operation USB_5 V USB_3.3 V USB_3 I Device supply current in device USB_Configured active mode, bus clock and IMO = 24 MHz I Device supply current ...

Page 103

Memory Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.4.1 Flash Table 11-58. Flash DC Specifications Parameter Description Erase and program voltage Table 11-59. Flash AC Specifications Parameter Description T ...

Page 104

EEPROM Table 11-60. EEPROM DC Specifications Parameter Description Erase and program voltage Table 11-61. EEPROM AC Specifications Parameter Description T Single row erase/write cycle time WRITE EEPROM data retention time, retention period measured from last erase cycle 11.4.3 Nonvolatile ...

Page 105

External Memory Interface Figure 11-67. Asynchronous Read Cycle Timing EM_ CEn Taddrv EM_ Addr EM_ OEn EM_ WEn EM_ Data Document Number: 001-11729 Rev. *R PSoC Tcel Address Toel Tdoesu Tdoeh Data ® 3: CY8C38 Family Data Sheet Taddrh ...

Page 106

Table 11-66. Asynchronous Read Cycle Specifications Parameter Description [46] T EMIF clock period Tcel EM_CEn low time Taddrv EM_CEn low to EM_Addr valid Taddrh Address hold time after EM_Wen high Toel EM_OEn low time Tdoesu Data to EM_OEn high setup ...

Page 107

EM_ Clock EM_ CEn EM_ Addr EM_ OEn EM_ Data EM_ ADSCn Table 11-68. Synchronous Read Cycle Specifications Parameter Description [47] T EMIF clock period Tcp/2 EM_Clock pulse high Tceld EM_CEn low to EM_Clock high Tcehd EM_Clock high to EM_CEn ...

Page 108

EM_ Clock EM_ CEn EM_ Addr EM_ WEn EM_ Data EM_ ADSCn Table 11-69. Synchronous Write Cycle Specifications Parameter Description [48] T EMIF clock Period Tcp/2 EM_Clock pulse high Tceld EM_CEn low to EM_Clock high Tcehd EM_Clock high to EM_CEn ...

Page 109

PSoC System Resources Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.5.1 POR with Brown Out For brown out detect in regulated mode, V mode. Table 11-70. Precise Power On ...

Page 110

Interrupt Controller Table 11-74. Interrupt Controller AC Specifications Parameter Description Delay from interrupt signal input to ISR code execution from ISR code 11.5.4 JTAG Interface TCK T_TDI_setup TDI TDO T_TMS_setup TMS Table 11-75. JTAG Interface AC Specifications Parameter Description ...

Page 111

SWD Interface SWDCK SWDIO (PSoC 3 reading on SWDIO) SWDIO (PSoC 3 writing to SWDIO) Table 11-76. SWD Interface AC Specifications Parameter Description f_SWDCK SWDCLK frequency T_SWDI_setup SWDIO input setup before SWDCK high T = 1/f_SWDCK max T_SWDI_hold SWDIO ...

Page 112

Clocking Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. Unless otherwise specified, all charts and graphs show typical values. 11.6.1 32 kHz External Crystal Table 11-78. 32 kHz External Crystal ...

Page 113

Table 11-81. IMO AC Specifications Parameter Description IMO frequency stability (with factory trim) 62.6 MHz 48 MHz 24 MHz – Non USB mode F IMO 24 MHz – USB mode 12 MHz 6 MHz 3 MHz [54] Startup time [54] ...

Page 114

Internal Low-Speed Oscillator Table 11-82. ILO DC Specifications Parameter Description Operating current I CC Leakage current Table 11-83. ILO AC Specifications Parameter Description Startup time, all frequencies ILO frequencies (trimmed) 100 kHz 1 kHz F ILO ILO frequencies (untrimmed) ...

Page 115

External Crystal Oscillator Table 11-84. ECO AC Specifications Parameter Description F Crystal frequency range 11.6.5 External Clock Reference Table 11-85. External Clock Reference AC Specifications Parameter Description External frequency range Input duty cycle range Input edge rate 11.6.6 Phase-Locked ...

Page 116

... Del-Sig CY8C3866LTI-023 – 20-bit Del-Sig CY8C3866LTI-067 – 20-bit Del-Sig CY8C3866PVI-021 – 20-bit Del-Sig ✔ CY8C3866AXI-038 20-bit Del-Sig ✔ CY8C3866LTI-029 20-bit Del-Sig ✔ CY8C3866LTI-065 20-bit Del-Sig ✔ CY8C3866PVI-066 20-bit Del-Sig Notes 59. Analog blocks support a variety of functionality including TIA, PGA, and mixers. See the can be used ...

Page 117

... Table 12-1. CY8C38 Family with Single Cycle 8051 (continued) MCU Core Part Number ✔ CY8C3866AXI-039 20-bit Del-Sig ✔ CY8C3866LTI-030 20-bit Del-Sig ✔ CY8C3866LTI-068 20-bit Del-Sig ✔ CY8C3866PVI-069 20-bit Del-Sig ✔ CY8C3866AXI-040 20-bit Del-Sig CY8C3866PVI-047 – 20-bit Del-Sig ✔ CY8C3866PVI-070 20-bit Del-Sig CY8C3866AXI-055 – 20-bit Del-Sig ✔ CY8C3866AXI-035 ...

Page 118

Part Numbering Conventions PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric ( … …, Z) unless stated otherwise. CY8Cabcdefg-xxx a: Architecture 3: PSoC 3 5: PSoC ...

Page 119

Packaging Table 13-1. Package Characteristics Parameter Description T Operating ambient temperature A T Operating junction temperature J Package θJA (48-pin SSOP) Tja Package θJA (48-pin QFN) Tja Package θJA (68-pin QFN) Tja Package θJA (100-pin TQFP) Tja Package θJC ...

Page 120

Figure 13-1. 48-pin (300 mil) SSOP Package Outline 24 25 0.620 0.630 0.088 0.092 0.025 BSC TOP VIEW 7.00±0. PIN 1 DOT LASER MARK NOTES: 1. HATCH AREA IS SOLDERABLE EXPOSED METAL. 2. REFERENCE ...

Page 121

Figure 13-3. 68-pin QFN 8×8 with 0.4 mm Pitch Package Outline (Sawn Version) TOP VIEW 8.000±0.100 PIN 1 DOT LASER MARK NOTES: 1. HATCH AREA IS SOLDERABLE EXPOSED METAL. 2. REFERENCE JEDEC#: MO-220 ...

Page 122

Acronyms Table 14-1. Acronyms Used in this Document Acronym Description abus analog local bus ADC analog-to-digital converter AG analog global AHB AMBA (advanced microcontroller bus archi- tecture) high-performance bus, an ARM data transfer bus ALU arithmetic logic unit AMUXBUS ...

Page 123

Table 14-1. Acronyms Used in this Document (continued) Acronym Description PHUB peripheral hub PHY physical layer PICU port interrupt control unit PLA programmable logic array PLD programmable logic device, see also PAL PLL phase-locked loop PMDD package material declaration data ...

Page 124

Table 16-1. Units of Measure (continued) Symbol Unit of Measure µF microfarads µH microhenrys µs microseconds µV microvolts µW microwatts mA milliamperes ms milliseconds mV millivolts nA nanoamperes ns nanoseconds nV nanovolts Ω ohms pF picofarads ppm parts per million ...

Page 125

Revision History ® Description Title: PSoC 3: CY8C38 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-11729 Submission Rev. ECN No. Date ** 571504 See ECN *A 754416 See ECN *B 2253366 See ECN *C 2350209 See ECN *D ...

Page 126

Description Title: PSoC 3: CY8C38 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-11729 *K 2903576 04/01/2010 Document Number: 001-11729 Rev. *R MKEA Updated Vb pin in PCB Schematic. Updated Tstartup parameter in AC Specifications table. Added Load regulation ...

Page 127

Description Title: PSoC 3: CY8C38 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-11729 *L 2938381 05/27/10 *M 2958674 06/22/10 *N 2989685 08/04/10 *O 3078568 11/04/10 *P 3107314 12/10/2010 Document Number: 001-11729 Rev. *R MKEA Replaced V with V ...

Page 128

Description Title: PSoC 3: CY8C38 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-11729 *Q 3179219 22/02/2011 *R 3200146 03/28/2011 Document Number: 001-11729 Rev. *R MKEA Updated conditions for flash data retention time Updated 100-pin TQFP package spec. Updated ...

Page 129

... Cypress against all charges. Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement ...