ADSP-21160NCB-100 Analog Devices Inc, ADSP-21160NCB-100 Datasheet - Page 10

ADSP-21160NCB-100

Manufacturer Part Number

ADSP-21160NCB-100

Description

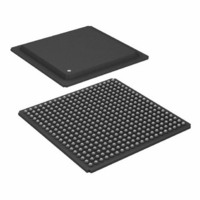

IC,DSP,32-BIT,CMOS,BGA,400PIN,PLASTIC

Manufacturer

Analog Devices Inc

Series

SHARC®r

Type

Floating Pointr

Specifications of ADSP-21160NCB-100

Rohs Status

RoHS non-compliant

Interface

Host Interface, Link Port, Serial Port

Clock Rate

100MHz

Non-volatile Memory

External

On-chip Ram

512kB

Voltage - I/o

3.30V

Voltage - Core

1.90V

Operating Temperature

-40°C ~ 100°C

Mounting Type

Surface Mount

Package / Case

400-BGA

Package

400BGA

Numeric And Arithmetic Format

Floating-Point

Maximum Speed

100 MHz

Ram Size

512 KB

Device Million Instructions Per Second

100 MIPS

Lead Free Status / RoHS Status

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADSP-21160NCB-100

Manufacturer:

Analog Devices Inc

Quantity:

10 000

ADSP-21160M/ADSP-21160N

Because the VDK is a library, a developer can decide whether to

use it or not. The VDK is integrated into the VisualDSP++

development environment, but can also be used via standard

command-line tools. When the VDK is used, the development

environment assists the developer with many error-prone tasks

and assists in managing system resources, automating the gen-

eration of various VDK-based objects, and visualizing the

system state, when debugging an application that uses the VDK.

Use the Expert Linker to visually manipulate the placement of

code and data on the embedded system. View memory utiliza-

tion in a color-coded graphical form, easily move code and data

to different areas of the DSP or external memory with the drag

of the mouse, examine run time stack and heap usage. The

Expert Linker is fully compatible with existing Linker Definition

File (LDF), allowing the developer to move between the graphi-

cal and textual environments.

Analog Devices DSP emulators use the IEEE 1149.1 JTAG Test

Access Port of the ADSP-21160x processor to monitor and con-

trol the target board processor during emulation. The emulator

provides full-speed emulation, allowing inspection and modifi-

cation of memory, registers, and processor stacks. Nonintrusive

in-circuit emulation is assured by the use of the processor’s

JTAG interface—the emulator does not affect target system

loading or timing.

In addition to the software and hardware development tools

available from Analog Devices, third parties provide a wide

range of tools supporting the ADSP-2116x processor family.

Hardware tools include ADSP-2116x processor PC plug-in

cards. Third-party software tools include DSP libraries, real-

time operating systems, and block diagram design tools.

DESIGNING AN EMULATOR-COMPATIBLE DSP

BOARD (TARGET)

The Analog Devices family of emulators are tools that every

DSP developer needs to test and debug hardware and software

systems. Analog Devices has supplied an IEEE 1149.1 JTAG

Test Access Port (TAP) on each JTAG DSP. The emulator uses

the TAP to access the internal features of the DSP, allowing the

developer to load code, set breakpoints, observe variables,

observe memory, and examine registers. The DSP must be

halted to send data and commands, but once an operation has

been completed by the emulator, the DSP system is set running

at full speed with no impact on system timing.

To use these emulators, the target board must include a header

that connects the DSP’s JTAG port to the emulator.

For details on target board design issues including mechanical

layout, single-processor connections, multiprocessor scan

chains, signal buffering, signal termination, and emulator pod

logic, see Analog Devices JTAG Emulation Technical Reference

(EE-68) on the Analog Devices website (ww.analog.com)—use

site search on “EE-68.” This document is updated regularly to

keep pace with improvements to emulator support.

Rev. B | Page 10 of 60 | February 2010

ADDITIONAL INFORMATION

This data sheet provides a general overview of the

ADSP-21160x architecture and functionality. For detailed infor-

mation on the Blackfin family core architecture and instruction

set, refer to the ADSP-21160 SHARC DSP Hardware Reference

and the ADSP-21160 SHARC DSP Instruction Set Reference. For

detailed information on the development tools for this proces-

sor, see the VisualDSP++ User’s Guide.