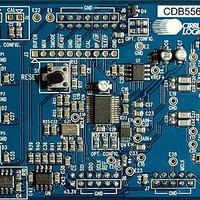

CDB5566 Cirrus Logic Inc, CDB5566 Datasheet - Page 15

CDB5566

Manufacturer Part Number

CDB5566

Description

Dev Bd For I/C 24-bit, Diff, 5kSPS, DAQ

Manufacturer

Cirrus Logic Inc

Type

A/Dr

Specifications of CDB5566

Number Of Adc's

1

Number Of Bits

24

Sampling Rate (per Second)

5k

Data Interface

SPI™

Inputs Per Adc

2 Differential

Input Range

0 ~ 4.096 V

Power (typ) @ Conditions

20mW @ 5kSPS

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

CS5566

Conversion Rate

5 KSPS

Resolution

24 bit

Maximum Clock Frequency

8 MHz

Interface Type

SPI

Supply Voltage (max)

3.3 V

Supply Voltage (min)

- 2.5 V

Product

Data Conversion Development Tools

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

CS5566

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

598-1557

CDB-5566

CDB-5566

3.2 Power Consumption

The power consumption of the CS5566 converter is a function of the conversion rate.

the typical power consumption of the converter when operating from either MCLK = 8 MHz or

MCLK = 4 MHz. The rate at which conversions are performed directly affects the power consumption.

When the converter is powered but not converting, it is in an idle state where its power consumption is

about 11 mW. When the CONV signal goes low to start a conversion, the converter delays the actual start

of conversion for 1182 to 1186 MCLK cycles, depending upon how CONV is controlled. The timing for the

conversion sequence is shown in

CONV goes low, the converter enters a higher-power state for 354 MCLK cycles and then returns to a

lower-power state for 64 MCLK cycles, after which the RDY signal falls to indicate the completion of a

conversion. Since the peak operating current for the converter occurs during the 354 MCLK, higher-pow-

er state, it is recommended that a large capacitor be used on the supply to the converter (as shown in

Figures 9 and 10). This capacitor filters the peak current demand from the power supply. The average

power consumption for the converter will depend upon the frequency of MCLK and the rate at which con-

versions are performed as illustrated in

DS806PP1

17.5

12.5

7.5

20

15

10

0

Figure 6. Power Consumption vs. Conversion Rate

500

1k

Figure 1

MCLK = 4MHz

Figure 1

1.5

on page 6. After the 1182 - 1186 MCLK delay from when

Word Rate (Sps)

3/25/08

2k 2.5k 3k 3.5k 4k 4.5k 5k

on page 6.

MCLK = 8MHz

Figure 6

CS5566

illustrates

15