CDB5566 Cirrus Logic Inc, CDB5566 Datasheet - Page 10

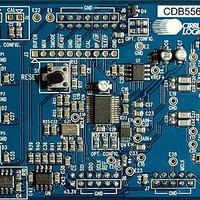

CDB5566

Manufacturer Part Number

CDB5566

Description

Dev Bd For I/C 24-bit, Diff, 5kSPS, DAQ

Manufacturer

Cirrus Logic Inc

Type

A/Dr

Specifications of CDB5566

Number Of Adc's

1

Number Of Bits

24

Sampling Rate (per Second)

5k

Data Interface

SPI™

Inputs Per Adc

2 Differential

Input Range

0 ~ 4.096 V

Power (typ) @ Conditions

20mW @ 5kSPS

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

CS5566

Conversion Rate

5 KSPS

Resolution

24 bit

Maximum Clock Frequency

8 MHz

Interface Type

SPI

Supply Voltage (max)

3.3 V

Supply Voltage (min)

- 2.5 V

Product

Data Conversion Development Tools

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

CS5566

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

598-1557

CDB-5566

CDB-5566

DIGITAL CHARACTERISTICS

T

DIGITAL FILTER CHARACTERISTICS

T

10

Input Leakage Current

Digital Input Pin Capacitance

Digital Output Pin Capacitance

Group Delay

A = TMIN to TMAX; VL = 3.3V, ±5% or VL = 2.5V, ±5% or 1.8V, ±5%; VLR = 0V

A = TMIN to TMAX; VL = 3.3V, ±5% or VL = 2.5V, ±5% or 1.8V, ±5%; VLR = 0V

SCLK(i)

MCLK

SDO

RDY

CS

16.

conversion cycle. See

See

Figure 4

Figure 5. SEC Mode - Discontinuous SCLK Read Timing (Not to Scale)

to understand conversion timing. The 160 MCLK group delay occurs during the 354 MCLK high-power period of a

Parameter

Parameter

t

17

Section 3.2 Power Consumption

t

MSB

15

t

18

t

19

3/25/08

(Note 16)

for more detail.

Symbol

Symbol

C

C

I

out

in

-

in

Min

Min

-

LSB

-

-

-

t

20

Typ

160

Typ

3

3

-

t

21

Max

Max

2

-

-

-

CS5566

DS806PP1

MCLKs

Unit

Unit

µA

pF

pF