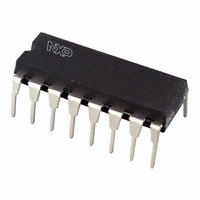

74HC40105N,652 NXP Semiconductors, 74HC40105N,652 Datasheet - Page 12

74HC40105N,652

Manufacturer Part Number

74HC40105N,652

Description

IC FIFO REGISTER 4X16 16DIP

Manufacturer

NXP Semiconductors

Series

74HCr

Datasheet

1.74HC40105DB118.pdf

(25 pages)

Specifications of 74HC40105N,652

Function

Asynchronous

Memory Size

64 (4 x 16)

Data Rate

25MHz

Voltage - Supply

2 V ~ 6 V

Mounting Type

Through Hole

Package / Case

16-DIP (0.300", 7.62mm)

Logic Family

HC

Logical Function

FIFO Register

Number Of Elements

1

Number Of Bits

4

Number Of Inputs

4

Number Of Outputs

4

High Level Output Current

-7.8mA

Low Level Output Current

7.8mA

Propagation Delay Time

750ns

Operating Supply Voltage (typ)

5V

Operating Supply Voltage (max)

6V

Operating Supply Voltage (min)

2V

Output Type

3-State

Polarity

Non-Inverting

Technology

CMOS

Frequency (max)

36(Typ)MHz

Mounting

Through Hole

Pin Count

16

Operating Temp Range

-40C to 125C

Operating Temperature Classification

Automotive

Quiescent Current

8uA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Operating Temperature

-

Access Time

-

Lead Free Status / Rohs Status

Compliant

Other names

74HC40105N

74HC40105N

933669660652

74HC40105N

933669660652

Philips Semiconductors

Master reset applied with FIFO full

Shifting out sequence; FIFO full to FIFO empty

1998 Jan 23

4-bit x 16-word FIFO register

(1) HC : V

Fig.8

(1) HC : V

Fig.9

HCT : V

HCT : V

Waveforms showing the MR input to DIR, DOR output

propagation delays and the MR pulse width.

Waveforms showing the SO input to DIR output propagation

delay. The SO pulse width and SO maximum pulse frequency.

M

M

M

M

= 50%; V

= 50%; V

= 1.3 V; V

= 1.3 V; V

I

I

I

I

= GND to V

= GND to V

= GND to 3 V.

= GND to 3 V.

CC

CC

.

.

12

Notes to Fig.8

1. DIR LOW, output ready HIGH;

2. MR pulse HIGH; clears FIFO.

3. DIR goes HIGH; flag indicates

4. DOR drops LOW; flag indicates

Notes to Fig.9

1. DOR HIGH; no data transfer in

2. SO set HIGH.

3. SO is set LOW; data in the input

4. DOR drops LOW; output stage

5. DOR goes HIGH; transfer

6. Repeat process to unloaded the

7. DOR remains LOW; FIFO is

assume FIFO is full.

input prepared for valid data.

FIFO empty.

progress, valid data is present at

output stage.

stage is unloaded, and new data

replaces it as empty location

“bubbles-up” to input stage.

“busy”.

process completed, valid data

present at output after the

specified propagation delay.

3rd through to the 16th word from

FIFO.

empty.

74HC/HCT40105

Product specification