XE8000EV110 Semtech, XE8000EV110 Datasheet - Page 106

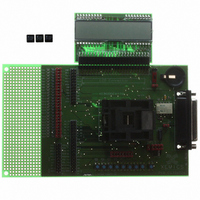

XE8000EV110

Manufacturer Part Number

XE8000EV110

Description

EVAL BOARD FOR XE8802AMI035LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV110

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC02MI035

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 106 of 193

- Download datasheet (2Mb)

Block configuration registers:

Note that the precision of the 4kHz depends on the selected clock source (see documentation of the clock block).

In slave mode, the fastest clock of the circuit should be at least 4 times faster than the baud rate of the master.

© Semtech 2006

7

6

5

4

3

2

1-0

7-3

2

1

0

7-0

Pos.

pos.

pos.

ClearCounter

SpiEnable

ClockPhase

ClockPolarity

SpiDataOut[7:0]

NotSlaveSelect

SpiMaster

BaudRate

--

SpiOverflow

SpiRxFull

SpiTxEmpty

RegSpiDataOut

RegSpiControl

RegSpiStatus

r/w

w1

r/w

r/w

r/w

r/w

r/w

r/w

r

r

c1

r

r

w1

Rw

Rw

Rw

00000000

-

1 nresetglobal

1 nresetglobal

0 nresetglobal

1 nresetglobal

0 nresetglobal

00

nresetglobal

00000

0

nresetglobal

0

nresetglobal

1

nresetglobal

nresetglobal

XE8802 Sensing Machine Data Acquisition MCU

Table 16-5: RegSpiDataOut

Table 16-3: RegSpiControl

Table 16-4: RegSpiStatus

Reset

Reset

Reset

16-3

Writing 1 clears transmission control counters.

In master mode, this bit drives the NSS output

pad. Unused in slave mode. It must be

asserted (to 0) during a byte transfer.

0: SPI slave mode.

1: SPI master mode.

peripheral configuration:

0: general purpose digital I/O port

1: SPI interface

Controls the timing relationship between the

serial clock and SPI data (cf. Figure 16-2 and

Figure 16-3).

Determines the idle-state of the SPI clock

signal (cf. Figure 16-2 and Figure 16-3).

Selects the baud rate in master mode.

00 => ckRcExt/2

01 => ckRcExt/8

10 => ckRcExt/16

11 => 4kHz

Unused

This flag is set when a new byte is loaded in

SpiDataIn before the previous byte was read.

Writing 1 clears the flag.

This flag is set each time a byte transfers from

the shift register to SpiDataIn. It is cleared by

reading SpiDataIn.

This flag is cleared each time the CPU writes a

byte in SpiDataOut. It is set when a byte

transfers from SpiDataOut to the shift register.

In the master mode, writing 1 to this bit

performs the data transfer SpiDataOut to the

shift

transmission.

In the slave mode, the byte transfer is done

automatically except for the very first byte

after nresetglobal (cf.16.6 Software hints).

SPI mode: transmission data buffer

I/O mode: output data (only bits 3:0, see Table

16-2)

with ZoomingADC™ and LCD driver

register

and

Function

Function

Function

enables

the

start

www.semtech.com

of

Related parts for XE8000EV110

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: