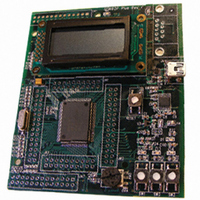

QSK-62P PLUS BNS Solutions, QSK-62P PLUS Datasheet - Page 74

QSK-62P PLUS

Manufacturer Part Number

QSK-62P PLUS

Description

KIT QUICK START RENESAS 62P

Manufacturer

BNS Solutions

Series

M16C™r

Type

MCUr

Datasheet

1.QSK-62P_PLUS.pdf

(103 pages)

Specifications of QSK-62P PLUS

Contents

Board, Cable, CD

For Use With/related Products

M16C/62P

Lead Free Status / RoHS Status

Not applicable / Not applicable

Other names

867-1000

QSK-62P

QSK26A

QSK62P

QSK-62P

QSK26A

QSK62P

M16C/62P Group (M16C/62P, M16C/62PT)

Rev.2.41

REJ03B0001-0241

Switching Characteristics

(V

CC1

Table 5.48

NOTES:

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

d(BCLK-AD)

h(BCLK-AD)

h(RD-AD)

h(WR-AD)

d(BCLK-CS)

h(BCLK-CS)

h(RD-CS)

h(WR-CS)

d(BCLK-RD)

h(BCLK-RD)

d(BCLK-WR)

h(BCLK-WR)

d(BCLK-DB)

h(BCLK-DB)

d(DB-WR)

h(WR-DB)

d(BCLK-HLDA)

d(BCLK-ALE)

h(BCLK-ALE)

d(AD-ALE)

h(AD-ALE)

d(AD-RD)

d(AD-WR)

dz(RD-AD)

Symbol

1. Calculated according to the BCLK frequency as follows:

2. Calculated according to the BCLK frequency as follows:

3. Calculated according to the BCLK frequency as follows:

4. Calculated according to the BCLK frequency as follows:

= V

CC2

Jan 10, 2006

----------------------- - 10 ns

f BCLK

----------------------- -

f BCLK

----------------------- -

f BCLK

----------------------- - 15 ns

f BCLK

0.5x10

0.5x10

0.5x10

0.5x10

(

(

(

(

= 5V, V

Address Output Delay Time

Address Output Hold Time (in relation to BCLK)

Address Output Hold Time (in relation to RD)

Address Output Hold Time (in relation to WR)

Chip Select Output Delay Time

Chip Select Output Hold Time (in relation to BCLK)

Chip Select Output Hold Time (in relation to RD)

Chip Select Output Hold Time (in relation to WR)

RD Signal Output Delay Time

RD Signal Output Hold Time

WR Signal Output Delay Time

WR Signal Output Hold Time

Data Output Delay Time (in relation to BCLK)

Data Output Hold Time (in relation to BCLK)

Data Output Delay Time (in relation to WR)

Data Output Hold Time (in relation to WR)

HLDA Output Delay Time

ALE Signal Output Delay Time (in relation to BCLK)

ALE Signal Output Hold Time (in relation to BCLK)

ALE Signal Output Delay Time (in relation to Address)

ALE Signal Output Hold Time (in relation to Address)

RD Signal Output Delay From the End of Address

WR Signal Output Delay From the End of Address

Address Output Floating Start Time

9

9

9

9

access and multiplex bus selection)

Memory Expansion and Microprocessor Modes (for 2- to 3-wait setting, external area

)

)

)

)

–

–

–

–

50

40

SS

[

[

[

[

ns

ns

= 0V, at T

]

]

]

]

Page 72 of 96

n is “2” for 2-wait setting, “3” for 3-wait setting.

opr

Parameter

= −20 to 85°C / −40 to 85°C unless otherwise specified)

See

Figure 5.12

(NOTE 1)

(NOTE 1)

(NOTE 1)

(NOTE 1)

(NOTE 2)

(NOTE 1)

(NOTE 3)

(NOTE 4)

V

Min.

CC1

− 4

5. Electrical Characteristics

4

4

0

0

4

0

0

Standard

=V

Max.

50

50

40

40

50

40

25

8

CC2

=3V

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns