QSK-62P PLUS BNS Solutions, QSK-62P PLUS Datasheet - Page 33

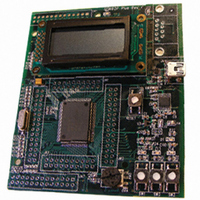

QSK-62P PLUS

Manufacturer Part Number

QSK-62P PLUS

Description

KIT QUICK START RENESAS 62P

Manufacturer

BNS Solutions

Series

M16C™r

Type

MCUr

Datasheet

1.QSK-62P_PLUS.pdf

(103 pages)

Specifications of QSK-62P PLUS

Contents

Board, Cable, CD

For Use With/related Products

M16C/62P

Lead Free Status / RoHS Status

Not applicable / Not applicable

Other names

867-1000

QSK-62P

QSK26A

QSK62P

QSK-62P

QSK26A

QSK62P

M16C/62P Group (M16C/62P, M16C/62PT)

Rev.2.41

REJ03B0001-0241

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.8.1

2.8.2

2.8.3

2.8.4

2.8.5

2.8.6

2.8.7

The register A0 consists of 16 bits, and is used for address register indirect addressing and address register relative

addressing. They also are used for transfers and logic/logic operations. A1 is the same as A0.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

FB is configured with 16 bits, and is used for FB relative addressing.

INTB is configured with 20 bits, indicating the start address of an interrupt vector table.

PC is configured with 20 bits, indicating the address of an instruction to be executed.

Stack pointer (SP) comes in two types: USP and ISP, each configured with 16 bits.

Your desired type of stack pointer (USP or ISP) can be selected by the U flag of FLG.

SB is configured with 16 bits, and is used for SB relative addressing.

FLG consists of 11 bits, indicating the CPU status.

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

The D flag is used exclusively for debugging purpose. During normal use, it must be set to “0”.

This flag is set to “1” when an arithmetic operation resulted in 0; otherwise, it is “0”.

This flag is set to “1” when an arithmetic operation resulted in a negative value; otherwise, it is “0”.

Register bank 0 is selected when this flag is “0” ; register bank 1 is selected when this flag is “1”.

This flag is set to “1” when the operation resulted in an overflow; otherwise, it is “0”.

This flag enables a maskable interrupt.

Maskable interrupts are disabled when the I flag is “0”, and are enabled when the I flag is “1”. The I flag

is cleared to “0” when the interrupt request is accepted.

Address Registers (A0 and A1)

Frame Base Register (FB)

Interrupt Table Register (INTB)

Program Counter (PC)

User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

Static Base Register (SB)

Flag Register (FLG)

Jan 10, 2006

Carry Flag (C Flag)

Debug Flag (D Flag)

Zero Flag (Z Flag)

Sign Flag (S Flag)

Register Bank Select Flag (B Flag)

Overflow Flag (O Flag)

Interrupt Enable Flag (I Flag)

Page 31 of 96

2. Central Processing Unit (CPU)