AD8330-EVALZ Analog Devices Inc, AD8330-EVALZ Datasheet - Page 15

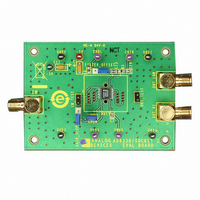

AD8330-EVALZ

Manufacturer Part Number

AD8330-EVALZ

Description

BOARD EVAL FOR AD8330

Manufacturer

Analog Devices Inc

Specifications of AD8330-EVALZ

Channels Per Ic

1 - Single

Amplifier Type

Variable Gain

Output Type

Differential, Rail-to-Rail

Slew Rate

1500 V/µs

-3db Bandwidth

150MHz

Operating Temperature

-40°C ~ 85°C

Current - Supply (main Ic)

20mA

Voltage - Supply, Single/dual (±)

2.7 V ~ 6 V

Board Type

Fully Populated

Utilized Ic / Part

AD8330

Silicon Manufacturer

Analog Devices

Application Sub Type

Variable Gain Amplifier

Kit Application Type

Amplifier

Silicon Core Number

AD8330

Kit Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Output / Channel

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Normal Operating Conditions

To minimize confusion, normal operating conditions are

defined as follows:

The input pins are voltage driven (the source impedance is

The output pins are open circuited (the load impedance is

Pin VMAG is unconnected setting up the output bias current

Pin CMGN is grounded.

MODE is either tied to a logic high or left unconnected, to set

The effects of other operating conditions are considered

separately.

Throughout this data sheet, the end-to-end voltage gain for the

normal operating conditions is referred to as the basic gain.

Under these conditions, it runs from 0 dB when V

(where this voltage is more exactly measured with reference

to Pin CMGN, which is not necessarily tied to ground) up to

50 dB for V

VDBS pin is driven below ground or above its nominal full-

scale value.

The input is accepted at the INHI/INLO differential port. These

pins are internally biased to roughly the midpoint of the supply,

V

V

mode value, from zero to V

interface provides good common-mode rejection up to high

frequencies (see Figure 16) and, thus, can be driven in either a

single-sided or differential manner. However, operation using a

differential drive is preferable, and this is assumed in the

specifications, unless otherwise stated.

The pin-to-pin input resistance is specified as 950 Ω ± 20%. The

driving-point impedance of the signal source can range from

zero up to values considerably in excess of this resistance, with a

corresponding variation in noise figure (see Figure 53). In most

cases, the input is coupled via two capacitors, chosen to provide

adequate low frequency transmission. This results in the minimum

input noise that increases when some other common-mode volt-

age is forced onto these pins. The short-circuit, input-referred

noise at maximum gain is approximately 5 nV/√Hz.

Output Pin OPHI and Output Pin OPLO operate at a common-

mode voltage at the midpoint of the supply, V

millivolts. This ensures that an analog-to-digital converter

(ADC) attached to these outputs operates within the often

narrow range permitted by their design. When a common-

mode voltage other than V

easily be forced by applying an externally provided voltage to

the output centering pin, CNTR. This voltage can run from zero

to the full supply, though the use of such extreme values leaves

only a small range for the differential output signal swing.

S

S

(it is actually ~2.75 V for V

= 3 V), but the AD8330 is able to accept a forced common-

assumed to be zero).

assumed to be infinite).

(I

the up gain mode.

N

in the four-transistor gain cell) to its nominal value.

DBS

= 1.5 V. The gain does not fold over when the

S

S

/2 is required at this interface, it can

, with certain limitations. This

S

= 5 V, V

DBS

= 0 V, and 1.5 V for

S

/2, within a few

DBS

= 0 V

Rev. E | Page 15 of 32

The differential impedance measured between OPHI and

OPLO is 150 Ω ± 20%. It follows that both the gain and the

full-scale voltage swing depend on the load impedance; both are

nominally halved when this is also 150 Ω. A fixed impedance

output interface, rather than an op amp style voltage-mode

output, is preferable in high speed applications because the

effects of complex reactive loads on the gain and phase can be

better controlled. The top end of the AD8330 ac response is

optimally flat for a 12 pF load on each pin, but this is not

critical, and the system remains stable for any value of load

capacitance including zero.

Another useful feature of this VGA in connection with the

driving of an ADC is that the peak output magnitude can be

precisely controlled by the voltage on Pin VMAG. Usually, this

voltage is internally preset to 500 mV, and the peak differential

unloaded output swing is ±2 V ± 3%. However, any voltage

from zero to at least 5 V can be applied to this pin to alter the

peak output in an exactly proportional way. Because either

output pin can swing rail-to-rail, which in practice means down

to at least 0.35 V and to within the same voltage below the

supply, the peak-to-peak output between these pins can be as

high as 10 V using V

Linear-in-dB Gain Control (V

All Analog Devices, Inc., VGAs featuring a linear-in-dB gain

law, such as the X-AMP® family, provide exact, constant gain

scaling over the fully specified gain range, and the deviation

from the ideal response is within a small fraction of a dB. For

the AD8330, the scaling of both of its gain interfaces is

substantially independent of process, supply voltage, or

temperature. The basic gain, G

where V

Alternatively, this can be expressed as a numerical gain

magnitude

COMM

MODE

VDBS

V

VPSI

INLO

DBS

INHI

LINEAR-IN-dB

INTERFACE

G

500Ω

500Ω

B

( )

DBS

dB

is in volts.

=

Figure 47. Schematic of Key Components

30

V

ΔV = 0

DBS

mV

12.65µA–4mA OR

4mA–12.65µA

S

= 6 V.

CM MODE

FEEDBACK

B

, is simply

TRANSIMPEDANCE

OUTPUT STAGE

DBS

)

ΔV = 0

MAGNITUDE

INTERFACE

AD8330

R

OUT =

O/P CM-MODE

NORMALLY

AT V

5kΩ

150Ω

P

100µA

/2

CNTR

COMM

VMAG

V

VPSO

OPLO

OPHI

MAG

(1)