lh28f800bje-pttlz1 Sharp Microelectronics of the Americas, lh28f800bje-pttlz1 Datasheet - Page 40

lh28f800bje-pttlz1

Manufacturer Part Number

lh28f800bje-pttlz1

Description

Manufacturer

Sharp Microelectronics of the Americas

Datasheet

1.LH28F800BJE-PTTLZ1.pdf

(47 pages)

- Current page: 40 of 47

- Download datasheet (524Kb)

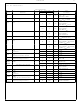

6.2.6 Alternative CE#-Controlled Writes

NOTES:

1. In systems where CE# defines the write pulse width (within a longer WE# timing waveform), all setup, hold, and inactive

2. Sampled, not 100% tested.

3. Refer to Table 4 for valid A

4. V

5. If BYTE# switch during reading cycle, exist the regulations separately.

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

AVAV

PHEL

WLEL

ELEH

SHEH

VPEH

AVEH

DVEH

EHDX

EHAX

EHWH

EHEL

EHRL

EHGL

QVVL

QVSL

FVEH

EHFV

Sym.

WE# times should be measured relative to the CE# waveform.

configuration success (SR.1/3/4/5=0).

CCW

should be held at V

Write Cycle Time

RP# High Recovery to CE# Going Low

WE# Setup to CE# Going Low

CE# Pulse Width

WP#V

V

Address Setup to CE# Going High

Data Setup to CE# Going High

Data Hold from CE# High

Address Hold from CE# High

WE# Hold from CE# High

CE# Pulse Width High

CE# High to RY/BY# Going Low or SR.7 Going "0"

Write Recovery before Read

V

WP# V

BYTE# Setup to CE# Going High

BYTE# Hold from CE# High

CCW

CCW

IH

Hold from Valid SRD, RY/BY# High Z

Setup to CE# Going High

IH

Setup to CE# Going High

Hold from Valid SRD, RY/BY# High Z

CCWH1/2

IN

and D

Parameter

until determination of block erase, full chip erase, word/byte write or lock-bit

IN

for block erase, full chip erase, word/byte write or lock-bit configuration.

V

CC

=3.1V-3.5V, T

(1)

A

=0°C to +70°C

Notes

2,4

2,4

2

2

2

3

3

5

5

Min.

100

100

70

50

50

50

30

50

70

1

0

0

0

0

0

0

0

Max.

100

Rev. 1.27

Unit

ns

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Related parts for lh28f800bje-pttlz1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

8 M-bit (512 kB x 16) SmartVoltage Flash Memories

Manufacturer:

Sharp Electrionic Components

Datasheet:

Part Number:

Description:

Transistor,bjt,array,darlington,45v V Br Ceo,400ma I C ,dip

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Single-chip Driver K/320 K-pixel Ccds With Dual-power-supply Operation

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Single-chip Driver K/320 Pixel Ccds With Dual-power-supply Operation

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Flash Memory 16mbit 2mbitx8

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Variable Output, Surface Mount Type Power-loss Voltage Regulators

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Voltage Operation Power-loss Voltage Regulator

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Voltage Operation Power-loss Voltage Regulator

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Variable Output, Compact Surface Mount Type Power-loss Voltage Regulators

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Stacked Chip Flash Memory Sram

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Pulse Dialer Cmos

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Tone Dialer

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

High Isolation Voltage Type, General Purpose Photocoupler

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

High Sensitivity, High Output Type Photocoupler

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet:

Part Number:

Description:

Pulse Tone Dialer

Manufacturer:

Sharp Microelectronics of the Americas

Datasheet: