PX1011B-EL1/G,551 NXP Semiconductors, PX1011B-EL1/G,551 Datasheet - Page 28

PX1011B-EL1/G,551

Manufacturer Part Number

PX1011B-EL1/G,551

Description

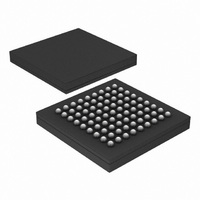

IC PCI-EXPRESS X1 PHY 81-LFBGA

Manufacturer

NXP Semiconductors

Specifications of PX1011B-EL1/G,551

Package / Case

81-LFBGA

Applications

PCI Express MAX to PCI Express PHY

Interface

JTAG

Voltage - Supply

1.2 V

Mounting Type

Surface Mount

Input Voltage Range (max)

0.31 V

Maximum Operating Temperature

+ 70 C

Maximum Power Dissipation

300 mW

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Operating Supply Voltage

1.2 V

Supply Current (max)

28 mA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

568-4715

935282113551

PX1011B-EL1/G-S

PX1011B-EL1/G-S

935282113551

PX1011B-EL1/G-S

PX1011B-EL1/G-S

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PX1011B-EL1/G,551

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

15. Abbreviations

16. References

17. Revision history

Table 23.

PX1011B_4

Product data sheet

Document ID

PX1011B_4

Modifications:

PX1011B_3

Modifications:

PX1011B_2

PX1011B_1

Revision history

Release date

20090904

20081020

20080319

20080213

•

•

Section

Added type number PX1011B-EL1/N (affects Section 2.6 “Miscellaneous”, Table 2 “Ordering

information”, (new) Table 3 “Leaded package marking”, Figure 2 “Pin configuration for LFBGA81”)

Table 22.

[1]

[2]

Acronym

BER

BIST

CMOS

CRC

EMI

ESD

FPGA

LTSSM

MAC

P2S

PCI

PCS

PHY

PLL

PIPE

PVT

S2P

SerDes

SKP

SSTL_2

PCI Express Base Specification — Rev. 1.0a - PCISIG

PHY Interface for the PCI Express Architecture (PIPE) Specification Version

1.00 — Intel Corporation

14: Errata information added

Abbreviations

Data sheet status

Product data sheet

Product data sheet

Product data sheet

Objective data sheet

Description

Bit Error Rate

Built-In Self Test

Complementary Metal Oxide Semiconductor

Cyclic Redundancy Check

ElectroMagnetic Interference

ElectroStatic Discharge

Field Programmable Gate Array

Link Training and Status State Machine

Media Access Control

Parallel to Serial

Peripheral Component Interconnect

Physical Coding Sub-layer

PHYsical layer

Phase-Locked Loop

PHY Interface for the PCI Express

Process Voltage Temperature

Serial to Parallel

Serializer and De-serializer

SKiP

Stub Series Terminated Logic for 2.5 Volts

Rev. 04 — 4 September 2009

Change notice

-

-

-

-

PCI Express stand-alone X1 PHY

Supersedes

PX1011B_3

PX1011B_2

PX1011B_1

-

PX1011B

© NXP B.V. 2009. All rights reserved.

28 of 30