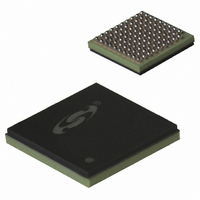

SI5364-G-BC Silicon Laboratories Inc, SI5364-G-BC Datasheet - Page 20

SI5364-G-BC

Manufacturer Part Number

SI5364-G-BC

Description

IC PREC PORT CARD CLOCK 99CBGA

Manufacturer

Silicon Laboratories Inc

Type

Clock Generatorr

Datasheet

1.SI5364-H-GL.pdf

(38 pages)

Specifications of SI5364-G-BC

Package / Case

99-CBGA

Pll

Yes

Input

Clock

Output

CML

Number Of Circuits

1

Ratio - Input:output

3:4

Differential - Input:output

Yes/Yes

Frequency - Max

675MHz

Divider/multiplier

No/Yes

Voltage - Supply

3.135 V ~ 3.465 V

Operating Temperature

-20°C ~ 85°C

Mounting Type

Surface Mount

Frequency-max

675MHz

Mounting Style

SMD/SMT

Operating Supply Voltage

2.3 V to 3.3 V

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

336-1280

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI5364-G-BC

Manufacturer:

LATTICE

Quantity:

190

Company:

Part Number:

SI5364-G-BC

Manufacturer:

SILICON

Quantity:

748

Company:

Part Number:

SI5364-G-BC

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

SI5364-G-BC

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

Si5364

2.6. 8 kHz Frame Sync

The Si5364 FSYNC output provides a sync pulse output

stream at an 8 kHz nominal rate. The frequency is

derived by dividing down the VCO clock output

frequency. The FSYNC output pulse stream is time

aligned by providing a rising edge on the SYNCIN input

pin. See Figure 3 on page 6. The FSYNC output is

disabled when 255/238 FEC scaling of the clock output

frequencies is selected or when the DSBLFSYNC input

is active.

2.7. Reset

The Si5364 provides a Reset/Calibration pin, RSTN/

CAL, which resets the device and disables the outputs.

When the RSTN/CAL pin is driven low, the internal

circuitry enters into the reset mode, and all LVTTL

outputs are forced into a high impedance state. Also,

the CLKOUT_n+ and CLKOUT_n– pins are forced to a

nominal CML logic LOW and HIGH respectively (See

Figure 12). The FRQSEL_n[1:0] setting must be set to

01, 10, or 11 to enable this mode. This feature is useful

for in-circuit test applications. A low-to-high transition on

RSTN/CAL initializes all digital logic to a known

condition and initiates self-calibration of the DSPLL. At

the completion of self-calibration, the DSPLL begins to

lock to the clock input signal.

2.8. PLL Self-Calibration

The Si5364 achieves optimal jitter performance by

using self-calibration circuitry to set the VCO center

frequency and loop gain parameters within the DSPLL.

Internal circuitry generates self calibration automatically

on powerup or after a loss-of-power condition. Self-

calibration can also be manually initiated by a low-to-

20

Figure 12. CLKOUT_n± Equivalent Circuit,

100 Ω

RSTN/CAL asserted LOW

15 mA

V

DD

2.5 V

100 Ω

CLKOUT_n–

CLKOUT_n+

Rev. 2.5

high transition on the RSTN/CAL input.

Self-calibration should be manually initiated after

changing the state of the FEC[1:0] inputs. Whether

manually initiated or automatically initiated at powerup,

the self-calibration process requires the presence of a

valid input clock.

If the self-calibration is initiated without a valid clock

present, the device waits for a valid clock before

completing the self-calibration. The Si5364 clock output

is set to the lower end of the operating frequency range

while the device waits for a valid clock. After the clock

input is validated, the calibration process runs to

completion, the device locks to the clock input, and the

clock output shifts to its target frequency. Subsequent

losses of the input clock signal do not require re-

calibration. If the clock input is lost following self-

calibration, the device enters digital hold mode. When

the input clock returns, the device re-locks to the input

clock without performing a self-calibration. During the

calibration process, the output clock frequency is

indeterminate and may jump as high as 5% above the

final locked value.

2.9. Bias Generation Circuitry

The Si5364 uses an external resistor to set internal bias

currents. The external resistor generates precise bias

currents that significantly reduce power consumption

and variation compared with traditional implementations

that use an internal resistor. The bias generation

circuitry requires a 10 k Ω (1%) resistor connected

between REXT and GND.

2.10. Differential Input Circuitry

The Si5364 provides differential inputs for the CLKIN_A,

CLKIN_B, and REF/CLKIN_F clock inputs. These inputs

are internally biased to a voltage of V

on page 7) and are driven by differential or single-ended

driver circuits. The termination resistor is connected

externally as shown.

2.11. Differential Output Circuitry

The Si5364 uses current mode logic (CML) output

drivers to provide the clock outputs CLKOUT[3:0]. For

single-ended operation, leave one CLKOUT line

unconnected.

2.12. Power Supply Connections

The Si5364 incorporates an on-chip voltage regulator.

The

compensation circuit of one resistor and one capacitor

to ensure stability in all operating conditions.

Internally, the Si5364 V

on-chip voltage regulator input, and the V

supply power to the device’s LVTTL I/O circuitry. The

V

DD25

pins supply power to the core DSPLL circuitry

voltage

regulator

DD33

pins are connected to the

requires

ICM

DD33

an

(see Table 2

pins also

external