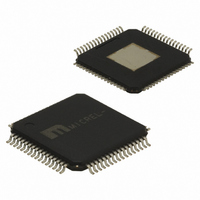

SY89538LHG TR Micrel Inc, SY89538LHG TR Datasheet - Page 12

SY89538LHG TR

Manufacturer Part Number

SY89538LHG TR

Description

IC SYNTHESIZR LVPECL/LVDS 64TQFP

Manufacturer

Micrel Inc

Series

Precision Edge®r

Type

Clock Synthesizer/Fanout Bufferr

Datasheet

1.SY89538LHH.pdf

(23 pages)

Specifications of SY89538LHG TR

Pll

Yes

Input

CMOS, HSTL, LVDS, LVPECL, LVTTL, SSTL, Crystal

Output

LVDS, LVPECL

Number Of Circuits

1

Ratio - Input:output

2:7

Differential - Input:output

Yes/Yes

Frequency - Max

756MHz

Divider/multiplier

Yes/No

Voltage - Supply

2.375 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

64-TQFP Exposed Pad, 64-eTQFP, 64-HTQFP, 64-VQFP

Frequency-max

756MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

SY89538LHGTR

SY89538LHGTR

SY89538LHGTR

Functional Description

Overall Function

The

synthesizer and fanout buffer with zero delay is part of

a precision PLL-based clock generation family

optimized for internal system clock generation

(FPGAs, ASICs, NPU).

Inputs

XTAL

The SY89538L features a fully integrated on-board

oscillator, which minimizes system implementation

cost. The oscillator is a series resonant, multi-vibrator

type crystal driver designed to drive a 14MHz to

18MHz series resonant crystal, see Table 6 and 7 for

more details on the crystal frequency range and

specifications.

June 2006

Frequency Range

(Fundamental Mode-

Series Resonant)

Frequency Tolerance

@ 25°C

Frequency Stability over

0°C to 70°C

Operating

Temperature Range

Storage

Temperature Range

Aging (per yr/1

Equivalent Series

Resistance (ESR)

Drive Level

Min.

14

Table 7. Quartz Crystal Oscillator Specifications

XTAL (MHz)

SY89538L

Table 6. XTAL Frequency Range and Valid

Max.

Programmable Range Table

st

18

3yrs)

integrated

X R

168

Min.

-40

-55

14

REF

programmable

Typ.

±30

±50

100

2.352

Min.

f

VCO

+125

Max.

±100

±50

+85

18

±5

50

(GHz)

3.024

Max.

Units

clock

PPM

PPM

PPM

MHz

µW

°C

°C

Ω

12

Oscillator Tips

Figure 2 below illustrates how to interface the crystal

with the SY89538L.

Quartz Crystal Selection:

Note: Raltron Series Resonant: AS-16.666-S-SMD-T-MI (2) Raltron

RFCK

The input MUX drives the PLLs phase detector, which

expects

94.5MHz. Therefore, reference clock maximum input

frequency is 756MHz when the reference divider is set

to a divide-by-8 and the reference clock minimum

frequency is 9.325MHz when the reference divider is

set to a divide-by-1. Given that the VCO frequency

range is from 2.352GHz to 3.024GHz, the minimum

and maximum frequency range of RFCK can be

calculated as follows:

Minimum Output Frequency (9.33MHz Input):

Maximum Output Frequency (756MHz Input):

1. Mount the crystal as close to the SY89538L

2. Mount the crystal on the same plane as the

3. To minimize noise pick up on the loop filter

4. Keep the crystal and its traces away from

f

f

f

f

f

OUT

OUT

OUT

OUT

OUT

as possible to minimize parasitic effects.

SY89538L to minimize on via hole inductance.

pins, cut the ground plane directly underneath

the loop filter component pads and traces.

adjacent noisy traces to minimize noise

coupling.

=

=

=

=

=

29

756

Pr

(

⎛

⎜

⎝

a

. 9

f

756

PHASE

4 .

33

eDivider

MHz

MHz

MHz

MHz

8

frequency

Figure 2. Crystal Interface

( ) ( ) ( )

( ) ( ) ( )

5

2

×

×

×

Pr

) (

⎞

⎟

⎠

×

hbwhelp@micrel.com

1

8

×

×

eDivider

63

PostDivide

×

×

(

8

×

×

2

2

2

2

) ( )

) ( )

×

×

×

2

2

between

FeedbackDi

r

×

(

Div

−

by

vider

−

9.325MHz

or (408) 955-1690

M9999-062706-D

2

)

and