KSZ8851-16MLL TR Micrel Inc, KSZ8851-16MLL TR Datasheet - Page 49

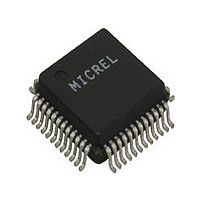

KSZ8851-16MLL TR

Manufacturer Part Number

KSZ8851-16MLL TR

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8851-16MLL_TR.pdf

(79 pages)

Specifications of KSZ8851-16MLL TR

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Lead Free Status / RoHS Status

Compliant

August 2009

Micrel, Inc.

Bit

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x0

0x0

0x0

0x1

0x0

0x0

0x0

0x0

0x0

0x0

0x0

0x0

0x0

0x0

0x0

Default Value

R/W

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Description

RXUDPFCC Receive UDP Frame Checksum Check Enable

When this bit is set, the KSZ8851 will check for correct UDP checksum for incoming UDP

frames. Any received UDP frames with incorrect checksum will be discarded.

RXTCPFCC Receive TCP Frame Checksum Check Enable

When this bit is set, the KSZ8851 will check for correct TCP checksum for incoming TCP

frames. Any received TCP frames with incorrect checksum will be discarded.

RXIPFCC Receive IP Frame Checksum Check Enable

When this bit is set, the KSZ8851 will check for correct IP header checksum for incoming

IP frames. Any received IP frames with incorrect checksum will be discarded.

RXPAFMA Receive Physical Address Filtering with MAC Address Enable

When this bit is set, this bit enables the RX function to receive physical address that pass

the MAC address filtering mechanism (see Address Filtering Scheme in Table 3 for

detail).

RXFCE Receive Flow Control Enable

When this bit is set and the KSZ8851-16MLL is in full-duplex mode, flow control is

enabled, and the KSZ8851-16MLL will acknowledge a PAUSE frame from the receive

interface; i.e., the outgoing packets are pending in the transmit buffer until the PAUSE

frame control timer expires. This field has no meaning in half-duplex mode and should be

programmed to 0.

When this bit is cleared, flow control is not enabled.

RXEFE Receive Error Frame Enable

When this bit is set, CRC error frames are allowed to be received into the RX queue.

When this bit is cleared, all CRC error frames are discarded.

RXMAFMA Receive Multicast Address Filtering with MAC Address Enable

When this bit is set, this bit enables the RX function to receive multicast address that pass

the MAC address filtering mechanism (see Address Filtering Scheme in Table 3 for

detail).

RXBE Receive Broadcast Enable

When this bit is set, the RX module receives all the broadcast frames.

RXME Receive Multicast Enable

When this bit is set, the RX module receives all the multicast frames (including broadcast

frames).

RXUE Receive Unicast Enable

When this bit is set, the RX module receives unicast frames that match the 48-bit Station

MAC address of the module.

RXAE Receive All Enable

When this bit is set, the KSZ8851-16MLL receives all incoming frames, regardless of the

frame’s destination address (see Address Filtering Scheme in Table 3 for detail).

Reserved

Reserved

RXINVF Receive Inverse Filtering

When this bit is set, the KSZ8851-16MLL receives function with address check operation

in inverse filtering mode (see Address Filtering Scheme in Table 3 for detail).

RXE Receive Enable

When this bit is set, the RX block is enabled and placed in a running state.

When this bit is cleared, the receive process is placed in the stopped state upon

completing reception of the current frame.

49

KSZ8851-16MLL/MLLI

M9999-083109-2.0