KSZ8851-16MLL TR Micrel Inc, KSZ8851-16MLL TR Datasheet - Page 23

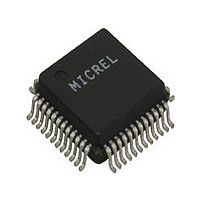

KSZ8851-16MLL TR

Manufacturer Part Number

KSZ8851-16MLL TR

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8851-16MLL_TR.pdf

(79 pages)

Specifications of KSZ8851-16MLL TR

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Lead Free Status / RoHS Status

Compliant

Clock Generator

The X1 and X2 pins are connected to a 25MHz crystal. X1 can also serve as the connector to a 3.3V, 25MHz oscillator

(as described in the pin description).

Bus Interface Unit (BIU)

The BIU host interface is a generic shared data bus interface, designed to communicate with embedded processors. No

glue logic is required when it talks to various standard asynchronous buses and processors.

Supported Transfers

In terms of transfer type, the BIU can support asynchronous transfer or SRAM-like slave mode. To support the data

transfers, the BIU provides a group of signals:

Shared Data bus SD[15:0] for Address, Data and Byte Enable, Command (CMD), Chip Select Enable (CSN), Read

(RDN), Write (WRN) and Interrupt (INTRN).

Physical Data Bus Size

The BIU supports an 8-bit or 16-bit host standard data bus. Depending on the size of the physical data bus, the KSZ8851-

16MLL can support 8-bit or 16-bit data transfers.

For example,

For a 16-bit data bus mode, the KSZ8851-16MLL allows an 8-bit and 16-bit data transfer.

For an 8-bit data bus mode, the KSZ8851-16MLL only allows an 8-bit data transfer.

The KSZ8851-16MLL supports internal data byte-swap. This means that the system/host data bus HD[7:0] just connect to

SD[7:0] for an 8-bit data bus interface. For a 16-bit data bus, the system/host data bus HD[15:8] and HD[7:0] only need to

connect to SD[15:8] and SD[7:0] respectively.

Table 4 describes the BIU signal grouping.

Little and Big Endian Support

The KSZ8851-16MLL supports either Little- or Big-Endian microprocessor. The external strap pin 10 (EESK) is used to

select between two modes. The KSZ8851-16MLL operates in Little Endian when this pin is pulled-down or in Big Endian

when this pin is pulled-up.

When this pin 10 is no connect or tied to GND, the bit 11 (Endian mode selection) in RXFDPR register can be used to

program either Little (bit11=0) Endian mode or Big (bit11=1) Endian mode.

August 2009

Micrel, Inc.

Signal

SD[15:0]

CMD

CSN

INTRN

RDN

WRN

Type

I/O

Input

Input

Output

Input

Input

Function

Shared Data Bus

Data D[15:0] -> SD[15:0] access when CMD=0. Address A[7:2] -> SD[7:2] and Byte Enable

BE[3:0] -> SD[15:12] access when CMD=1 in 16-bit mode. Address A[7:0] -> SD[7:0] only

access when CMD=1 in 8-bit mode (Shared data bus SD[15:8] must be tied to low in 8-bit bus

mode).

Command Type

This command input decides the SD[15:0] shared data bus access cycle information.

Chip Select Enable

Chip Enable asserted (low) indicates that the shared data bus access is enabled.

Interrupt

This pin is asserted to low when interrupt occurred.

Asynchronous Read

This pin is asserted to low during read cycle.

Asynchronous Write

This pin is asserted to low during write cycle.

Table 4. Bus Interface Unit Signal Grouping

23

KSZ8851-16MLL/MLLI

M9999-083109-2.0