KSZ8851-16MLL TR Micrel Inc, KSZ8851-16MLL TR Datasheet - Page 25

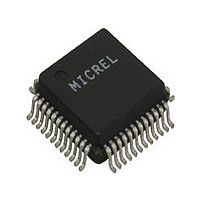

KSZ8851-16MLL TR

Manufacturer Part Number

KSZ8851-16MLL TR

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8851-16MLL_TR.pdf

(79 pages)

Specifications of KSZ8851-16MLL TR

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Lead Free Status / RoHS Status

Compliant

for the frame to transmit. The second word is used to specify the total number of bytes of the frame. The packet data

follows. The packet data area holds the frame itself. It may or may not include the CRC checksum depending upon

whether hardware CRC checksum generation is enabled in TXCR (bit 1) register.

Multiple frames can be pipelined in both the transmit queue and receive queue as long as there is enough queue memory,

thus avoiding overrun. For each transmitted frame, the transmit status information for the frame is located in the TXSR

(0x72) register.

Since multiple packets can be pipelined into the TX packet memory for transmit, the transmit status reflects the status of

the packet that is currently being transferred on the MAC interface, which may or may not be the last queued packet in the

TX queue.

The transmit control word is the first 16-bit word in the TX packet memory, followed by a 16-bit byte count. It must be word

aligned. Each control word corresponds to one TX packet. Table 6 gives the transmit control word bit fields.

The transmit Byte Count specifies the total number of bytes to be transmitted from the TXQ. Its format is given in Table 7.

The data area contains six bytes of Destination Address (DA) followed by six bytes of Source Address (SA), followed by a

variable-length number of bytes. On transmit, all bytes are provided by the CPU, including the source address. The

KSZ8851-16MLL does not insert its own SA. The 802.3 Frame Length word (Frame Type in Ethernet) is not interpreted by

the KSZ8851-16MLL. It is treated transparently as data both for transmit operations.

August 2009

Micrel, Inc.

Bit

15-11

10-0

Bit

15

14-6

5-0

Description

TXIC Transmit Interrupt on Completion

When this bit is set, the KSZ8851-16MLL sets the transmit interrupt after the present frame has been

transmitted.

Reserved.

TXFID Transmit Frame ID

This field specifies the frame ID that is used to identify the frame and its associated status information

in the transmit status register.

Description

Reserved.

TXBC Transmit Byte Count

Transmit Byte Count. Hardware uses the byte count information to conserve the TX buffer memory

for better utilization of the packet memory.

Note: The hardware behavior is unknown if an incorrect byte count information is written to this field.

Writing a 0 value to this field is not permitted.

Packet Memory

Address Offset

0

2

4 - up

Table 5. Frame Format for Transmit Queue

Table 6. Transmit Control Word Bit Fields

Table 7. Transmit Byte Count Format

Bit 15

2

Control Word

(High byte and low byte need to swap in Big-Endian

mode)

Byte Count

(High byte and low byte need to swap in Big-Endian

mode)

Transmit Packet Data

(maximum size is 2000)

nd

Byte

25

1

st

Bit 0

Byte

KSZ8851-16MLL/MLLI

M9999-083109-2.0