IPR-FIR Altera, IPR-FIR Datasheet - Page 5

IPR-FIR

Manufacturer Part Number

IPR-FIR

Description

IP CORE Renewal Of IP-FIR

Manufacturer

Altera

Type

MegaCorer

Specifications of IPR-FIR

Software Application

IP CORE, DSP Filters And Transforms

Supported Families

Arria GX, Arria II GX, Cyclone, HardCopy, Stratix

Core Architecture

FPGA

Core Sub-architecture

Arria, Cyclone, Stratix

Rohs Compliant

NA

Function

Finite Impulse Response Compiler

License

Renewal License

Lead Free Status / RoHS Status

na

Lead Free Status / RoHS Status

na

101 Innovation Drive

San Jose, CA 95134

(408) 544-7000

www.altera.com

Applications Hotline:

(800) 800-EPLD

Literature Services:

literature@altera.com

Altera Corporation

3.0.1

3.0.0

Version

Table 2. FIR Compiler MegaCore Function Revision History

Date

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company,

the stylized Altera logo, specific device designations, and all other words and logos that are identified as

trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera

Corporation in the U.S. and other countries. All other product or service names are the property of their re-

spective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products

to current specifications in accordance with Altera's standard warranty, but reserves the right to make chang-

es to any products and services at any time without notice. Altera assumes no responsibility or liability

arising out of the application or use of any information, product, or service described

herein except as expressly agreed to in writing by Altera Corporation. Altera customers

are advised to obtain the latest version of device specifications before relying on any pub-

lished information and before placing orders for products or services

Fixed bug in coefficient and data alignment for multi-channel multi-coefficient set

structure.

Fixed bug in data initialize file zero.hex for multichannel MCV structure which only

effect

Support for ModelSim simulation.

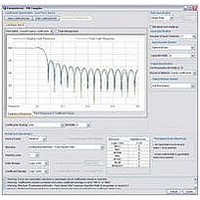

New Java based GUI with Multi-Platform support (Windows, Solaris, Linux)

Added Support for Stratix II Ternary Adders (with single rate distributed arithmetic

filters)

Dramatic speed increases and/or area reductions in Stratix II architecture

Serial FIR filters in Stratix II now achieve up to 350 MHz operation

Parallel Distributed Arithmetic FIR filters can achieve 320 MHz operation

Ternary adder structures combined with distributed arithmetic can

reduce area by 30%-50%

Added Atlantic based flow control and updated clock enable based flow control

circuitry

Added Filter Design Assistant (more messages to indicate which configurations

are supported and various error conditions)

Encrypted RTL Simulation is now replaced with IP Functional Simulation

Updated OpenCore Plus hardware evaluation encryption

Removed Visual IP Support

Removed all DSP Builder support

Removed support for older families (APEX, Mercury, ACEX, FLEX)

Updated report file - removed latency information

Auto scaling information (actual scaling factor) was displayed in an disabled edit

box in the older GUI. This information is no longer available.

Revision

.

Revision History

Preliminary

5