AT89C51SND2C-7FTUL Atmel, AT89C51SND2C-7FTUL Datasheet - Page 201

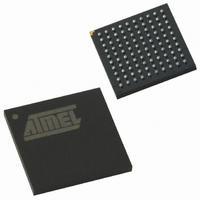

AT89C51SND2C-7FTUL

Manufacturer Part Number

AT89C51SND2C-7FTUL

Description

IC 8051 MCU FLASH 64K MP3 100BGA

Manufacturer

Atmel

Series

89Cr

Datasheet

1.AT89C51SND2C-7FTUL.pdf

(242 pages)

Specifications of AT89C51SND2C-7FTUL

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IDE/ATAPI, MMC, SPI, UART/USART, USB

Peripherals

Audio, I²S, MP3, PCM, POR, WDT

Number Of I /o

32

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.3 V

Data Converters

A/D 2x10b; D/A 2x20b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

ATAPI, I2S, IDE, SPI, UART, USB

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

32

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

AT89C51SND2C7FTUL

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51SND2C-7FTUL

Manufacturer:

ATMEL

Quantity:

4 371

- Current page: 201 of 242

- Download datasheet (3Mb)

22.1.4

22.1.5

22.1.6

4341H–MP3–10/07

Configuration

Conversion Launching

End Of Conversion

version (see Section "End Of Conversion", page 201). This bit is cleared by hardware at the end

of the conversion.

Notes:

The ADC configuration consists in programming the ADC clock as detailed in the Section "Clock

Generator", page 200. The ADC is enabled using the ADEN bit in ADCON register. As shown in

Figure 93, user must wait the setup time (T

Figure 22-4. ADC Configuration Flow

The conversion is launched by setting the ADSST bit in ADCON register, this bit remains set

during the conversion. As soon as the conversion is started, it takes 11 clock periods (T

before the data is available in ADDH and ADDL registers.

Figure 22-5. ADC Conversion Launching Flow

The end of conversion is signalled by the ADEOC flag in ADCON register becoming set or by the

ADSST bit in ADCON register becoming cleared. ADEOC flag can generate an interrupt if

1. Only the CPU activity is frozen, peripherals are not affected by the Pseudo-Idle mode.

2. If some interrupts occur during the Pseudo-Idle mode, they will be delayed and processed,

3. Concurrently with ADSST bit.

according to their priority after the end of the conversion.

Program ADC Clock

Conversion Start

ADCD4:0 = xxxxxb

Start Conversion

Wait Setup Time

Configuration

Select Channel

Enable ADC

SETUP

ADCS = 0-1

ADSST = 1

ADIDL = x

ADEN = 1

ADC

ADC

) before launching any conversion.

AT8xC51SND2C/MP3B

CONV

201

)

Related parts for AT89C51SND2C-7FTUL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: