ATSAM3U1CA-CU Atmel, ATSAM3U1CA-CU Datasheet - Page 1016

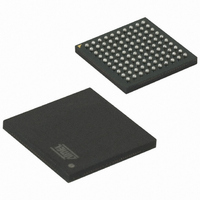

ATSAM3U1CA-CU

Manufacturer Part Number

ATSAM3U1CA-CU

Description

IC MCU 32BIT 64KB FLASH 100TFBGA

Manufacturer

Atmel

Series

SAM3Ur

Specifications of ATSAM3U1CA-CU

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

96MHz

Connectivity

EBI/EMI, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, I²S, POR, PWM, WDT

Number Of I /o

57

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

20K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 4x10b, 4x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

100

Processor Series

ATSAM3x

Core

ARM Cortex M3

Data Bus Width

32 bit

Data Ram Size

20 KB

Interface Type

3xUSART, TWI, 4xSPI, Bus

Maximum Clock Frequency

96 MHz

Number Of Programmable I/os

57

Number Of Timers

8

Operating Supply Voltage

1.62 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-CM3, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

ATSAM3U-EK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 1016 of 1171

- Download datasheet (25Mb)

1016

SAM3U Series

Buffer: A buffer of DMAC data. The amount of data (length) is determined by the flow controller.

For transfers between the DMAC and memory, a buffer is broken directly into a sequence of

AMBA bursts and AMBA single transfers.

For transfers between the DMAC and a non-memory peripheral, a buffer is broken into a

sequence of DMAC transactions (single and chunks). These are in turn broken into a sequence

of AMBA transfers.

Transaction: A basic unit of a DMAC transfer as determined by either the hardware or software

handshaking interface. A transaction is only relevant for transfers between the DMAC and a

source or destination peripheral if the source or destination peripheral is a non-memory device.

There are two types of transactions: single transfer and chunk transfer.

DMAC transfer: Software controls the number of buffers in a DMAC transfer. Once the DMAC

transfer has completed, then hardware within the DMAC disables the channel and can generate

an interrupt to signal the completion of the DMAC transfer. You can then re-program the channel

for a new DMAC transfer.

Single-buffer DMAC transfer: Consists of a single buffer.

Multi-buffer DMAC transfer: A DMAC transfer may consist of multiple DMAC buffers. Multi-buf-

fer DMAC transfers are supported through buffer chaining (linked list pointers), auto-reloading of

channel registers, and contiguous buffers. The source and destination can independently select

which method to use.

Channel locking: Software can program a channel to keep the AHB master interface by locking

the arbitration for the master bus interface for the duration of a DMAC transfer, buffer, or chunk.

Transfer

AMBA

Burst

Buffer

– Single transfer: The length of a single transaction is always 1 and is converted to a

– Chunk transfer: The length of a chunk is programmed into the DMAC. The chunk is

– Linked lists (buffer chaining) – A descriptor pointer (DSCR) points to the location

– Contiguous buffers – Where the address of the next buffer is selected to be a

single AMBA access.

then converted into a sequence of AHB access.DMAC executes each AMBA burst

transfer by performing incremental bursts that are no longer than 16 beats.

in system memory where the next linked list item (LLI) exists. The LLI is a set of

registers that describe the next buffer (buffer descriptor) and a descriptor pointer

register. The DMAC fetches the LLI at the beginning of every buffer when buffer

chaining is enabled.

continuation from the end of the previous buffer.

Transfer

AMBA

Burst

Buffer

HDMA Transfer

Transfer

AMBA

Burst

Buffer

Transfer

AMBA

Single

DMA Transfer

Level

Buffer Transfer

Level

AMBA Transfer

Level

6430D–ATARM–25-Mar-11

Related parts for ATSAM3U1CA-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM3U CORTEX

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

AT91 ARM Thumb-based Microcontrollers

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: