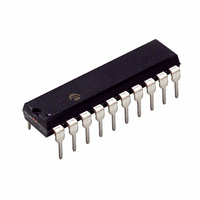

PIC16C770-I/P Microchip Technology, PIC16C770-I/P Datasheet - Page 88

PIC16C770-I/P

Manufacturer Part Number

PIC16C770-I/P

Description

IC MCU CMOS A/D 2K 20MHZ 20-DIP

Manufacturer

Microchip Technology

Series

PIC® 16Cr

Datasheets

1.PIC16C770-ISO.pdf

(220 pages)

2.PIC16C770-ISO.pdf

(6 pages)

3.PIC16C770-ISO.pdf

(8 pages)

Specifications of PIC16C770-I/P

Core Size

8-Bit

Program Memory Size

3.5KB (2K x 14)

Oscillator Type

Internal

Core Processor

PIC

Speed

20MHz

Connectivity

I²C, SPI

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

15

Program Memory Type

OTP

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 6x12b

Operating Temperature

-40°C ~ 85°C

Package / Case

20-DIP (0.300", 7.62mm)

Controller Family/series

PIC16C

No. Of I/o's

16

Ram Memory Size

256Byte

Cpu Speed

20MHz

No. Of Timers

3

No. Of

RoHS Compliant

Core

PIC

Processor Series

PIC16C

Data Bus Width

8 bit

Maximum Clock Frequency

20 MHz

Data Ram Size

256 B

Data Rom Size

256 B

On-chip Adc

6 bit

Number Of Programmable I/os

16

Number Of Timers

3 bit

Operating Supply Voltage

2.5 V to 5.5 V

Mounting Style

Through Hole

Height

3.3 mm

Interface Type

I2C, SPI, SSP

Length

26.16 mm

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4 V

Width

6.35 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

DVA16XP200 - ADAPTER ICE 20DIP/SOIC/SSOPAC164028 - MODULE SKT PROMATEII 20SOIC/DIP

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

PIC16C770I/P

PIC16C717/770/771

9.2.11

A Repeated START condition occurs when the RSEN

bit (SSPCON2<1>) is set high while the I

in the idle state. When the RSEN bit is set, the SCL pin

is asserted low. When the SCL pin is sampled low, the

baud rate generator is loaded with the contents of

SSPADD<6:0> and begins counting. The SDA pin is

released (brought high) for one baud rate generator

count (T

if SDA is sampled high, the SCL pin will be de-asserted

(brought high). When SCL is sampled high, the baud

rate generator is reloaded with the contents of

SSPADD<6:0> and begins counting. SDA and SCL

must be sampled high for one T

is then followed by assertion of the SDA pin (SDA is

low) for one T

a START condition is detected on the SDA and SCL

pins, the S bit (SSPSTAT<3>) will be set. Following

this, the baud rate generator is reloaded with the con-

tents of SSPAD<6:0> and begins counting. When the

BRG times out a third time, the RSEN bit in the

SSPCON2 register is automatically cleared and SCL is

pulled low. The SSPIF flag is set, which indicates the

Restart sequence is complete.

FIGURE 9-17:

DS41120B-page 86

Note 1: If RSEN is set while another event is in

BRG

2: A bus collision during the Repeated

I

START CONDITION TIMING

). When the baud rate generator times out,

progress, it will not take effect. Queuing of

events is not allowed.

2

START condition occurs if either of the

following is true:

a) SDA is sampled low when SCL

b) SCL goes low before SDA is

C MASTER MODE REPEATED

BRG

Falling edge of ninth clock

goes from low to high.

asserted low. This may indicate

that another master is attempting

to transmit a data “1”.

period while SCL is high. As soon as

REPEAT START CONDITION WAVEFORM

SDA

SCL

End of Xmit

BRG

Write to SSPCON2

occurs here.

SDA = 1,

SCL (no change)

period. This action

2

C module is

Advance Information

T

SDA = 1,

SCL = 1

BRG

T

BRG

Immediately following the SSPIF bit transition to true,

the user may write the SSPBUF with the 7-bit address

in 7-bit mode, or the default first address in 10-bit

mode. After the first eight bits are transmitted and an

ACK is received, the user may then perform one of the

following:

• Transmit an additional eight bits of address (if the

• Transmit eight bits of data (if the user transmitted

• Receive eight bits of data (if the user transmitted

9.2.11.1

If the user writes the SSPBUF when a Repeated

START sequence is in progress, then WCOL is set and

the contents of the buffer are unchanged (the write

doesn’t occur).

user transmitted the first half of a 10-bit address

with R/W = 0),

a 7-bit address with R/W = 0), or

either the first half of a 10-bit address or a 7-bit

address with R/W = 1).

Note:

Sr = Repeated START

T

BRG

At completion of START bit,

hardware clears RSEN bit

Set S (SSPSTAT<3>)

WCOL STATUS FLAG

Because queueing of events is not

allowed, writing of the lower five bits of

SSPCON2 is disabled until the Repeated

START condition is complete.

and sets SSPIF

Write to SSPBUF occurs here.

T

BRG

1st Bit

T

BRG

2002 Microchip Technology Inc.