MC9S12C128CFUE Freescale Semiconductor, MC9S12C128CFUE Datasheet - Page 398

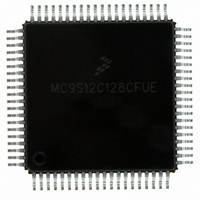

MC9S12C128CFUE

Manufacturer Part Number

MC9S12C128CFUE

Description

IC MCU 128K FLASH 25MHZ 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C128CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Cpu Family

HCS12

Device Core Size

16b

Frequency (max)

25MHz

Interface Type

CAN/SCI/SPI

Total Internal Ram Size

4KB

# I/os (max)

60

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

2.5/5V

Operating Supply Voltage (max)

2.75/5.5V

Operating Supply Voltage (min)

2.35/2.97V

On-chip Adc

8-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

80

Package Type

PQFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4000 B

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

61

Number Of Timers

1

Operating Supply Voltage

- 0.3 V to + 6.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

ST

Quantity:

6 246

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 398 of 690

- Download datasheet (4Mb)

Chapter 13 Serial Communications Interface (S12SCIV2) Block Description

writing another byte to the Transmitter buffer (SCIDRH/SCIDRL), while the shift register is still shifting

out the first byte.

To initiate an SCI transmission:

Writing the TE bit from 0 to a 1 automatically loads the transmit shift register with a preamble of 10 logic

1s (if M = 0) or 11 logic 1s (if M = 1). After the preamble shifts out, control logic transfers the data from

the SCI data register into the transmit shift register. A logic 0 start bit automatically goes into the least

significant bit position of the transmit shift register. A logic 1 stop bit goes into the most significant bit

position.

Hardware supports odd or even parity. When parity is enabled, the most significant bit (msb) of the data

character is the parity bit.

The transmit data register empty flag, TDRE, in SCI status register 1 (SCISR1) becomes set when the SCI

data register transfers a byte to the transmit shift register. The TDRE flag indicates that the SCI data

register can accept new data from the internal data bus. If the transmit interrupt enable bit, TIE, in SCI

control register 2 (SCICR2) is also set, the TDRE flag generates a transmitter interrupt request.

When the transmit shift register is not transmitting a frame, the Tx output signal goes to the idle condition,

logic 1. If at any time software clears the TE bit in SCI control register 2 (SCICR2), the transmitter enable

signal goes low and the transmit signal goes idle.

398

1. Configure the SCI:

2. Transmit Procedure for Each Byte:

3. Repeat step 2 for each subsequent transmission.

a) Select a baud rate. Write this value to the SCI baud registers (SCIBDH/L) to begin the baud

b) Write to SCICR1 to configure word length, parity, and other configuration bits

c) Enable the transmitter, interrupts, receive, and wake up as required, by writing to the SCICR2

a. Poll the TDRE flag by reading the SCISR1 or responding to the TDRE interrupt. Keep in mind

d) If the TDRE flag is set, write the data to be transmitted to SCIDRH/L, where the ninth bit is

rate generator. Remember that the baud rate generator is disabled when the baud rate is zero.

Writing to the SCIBDH has no effect without also writing to SCIBDL.

(LOOPS,RSRC,M,WAKE,ILT,PE,PT).

register bits (TIE,TCIE,RIE,ILIE,TE,RE,RWU,SBK). A preamble or idle character will now

be shifted out of the transmitter shift register.

that the TDRE bit resets to one.

written to the T8 bit in SCIDRH if the SCI is in 9-bit data format. A new transmission will not

result until the TDRE flag has been cleared.

The TDRE flag is set when the shift register is loaded with the next data to

be transmitted from SCIDRH/L, which happens, generally speaking, a little

over half-way through the stop bit of the previous frame. Specifically, this

transfer occurs 9/16ths of a bit time AFTER the start of the stop bit of the

previous frame.

MC9S12C-Family / MC9S12GC-Family

Rev 01.24

NOTE

Freescale Semiconductor

Related parts for MC9S12C128CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: