AT91SAM7XC256B-CU Atmel, AT91SAM7XC256B-CU Datasheet - Page 30

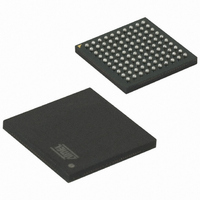

AT91SAM7XC256B-CU

Manufacturer Part Number

AT91SAM7XC256B-CU

Description

MCU ARM 256K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Datasheet

1.AT91SAM7XC128B-CU.pdf

(47 pages)

Specifications of AT91SAM7XC256B-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

91S

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

64 KB

Interface Type

CAN, Ethernet, SPI, TWI, USART, USB

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

9.5

9.6

9.7

9.8

30

Debug Unit

Periodic Interval Timer

Watchdog Timer

Real-time Timer

AT91SAM7XC512/256/128 Preliminary

• Vectoring

• Protect Mode

• Fast Forcing

• General Interrupt Mask

• Comprises:

• Two-pin UART

• Debug Communication Channel Support

• Chip ID Registers

• 20-bit programmable counter plus 12-bit interval counter

• 12-bit key-protected Programmable Counter running on prescaled SLCK

• Provides reset or interrupt signals to the system

• Counter may be stopped while the processor is in debug state or in idle mode

• 32-bit free-running counter with alarm running on prescaled SLCK

– Higher priority interrupts can be served during service of lower priority interrupt

– Optimizes interrupt service routine branch and execution

– One 32-bit vector register per interrupt source

– Interrupt vector register reads the corresponding current interrupt vector

– Easy debugging by preventing automatic operations

– Permits redirecting any interrupt source on the fast interrupt

– Provides processor synchronization on events without triggering an interrupt

– One two-pin UART

– One Interface for the Debug Communication Channel (DCC) support

– One set of Chip ID Registers

– One Interface providing ICE Access Prevention

– USART-compatible User Interface

– Programmable Baud Rate Generator

– Parity, Framing and Overrun Error

– Automatic Echo, Local Loopback and Remote Loopback Channel Modes

– Offers visibility of COMMRX and COMMTX signals from the ARM Processor

– Identification of the device revision, sizes of the embedded memories, set of

– Chip ID is 0x271C 0A40 (VERSION 0) for AT91SAM7XC512

– Chip ID is 0x271B 0940 (VERSION 0) for AT91SAM7XC256

– Chip ID is 0x271A 0740 (VERSION 0) for AT91SAM7XC128

peripherals

6209DS–ATARM–17-Feb-09