AT91SAM7XC256B-CU Atmel, AT91SAM7XC256B-CU Datasheet - Page 16

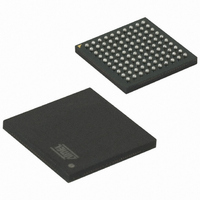

AT91SAM7XC256B-CU

Manufacturer Part Number

AT91SAM7XC256B-CU

Description

MCU ARM 256K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Datasheet

1.AT91SAM7XC128B-CU.pdf

(47 pages)

Specifications of AT91SAM7XC256B-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

91S

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

64 KB

Interface Type

CAN, Ethernet, SPI, TWI, USART, USB

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

7. Processor and Architecture

7.1

7.2

7.3

16

ARM7TDMI Processor

Debug and Test Features

Memory Controller

AT91SAM7XC512/256/128 Preliminary

• RISC processor based on ARMv4T Von Neumann architecture

• Two instruction sets

• Three-stage pipeline architecture

• Integrated embedded in-circuit emulator

• Debug Unit

• IEEE1149.1 JTAG Boundary-scan on all digital pins

• Programmable Bus Arbiter

• Address decoder provides selection signals for

• Abort Status Registers

• Misalignment Detector

• Remap Command

– Runs at up to 55 MHz, providing 0.9 MIPS/MHz

– ARM

– Thumb

– Instruction Fetch (F)

– Instruction Decode (D)

– Execute (E)

– Two watchpoint units

– Test access port accessible through a JTAG protocol

– Debug communication channel

– Two-pin UART

– Debug communication channel interrupt handling

– Chip ID Register

– Handles requests from the ARM7TDMI, the Ethernet MAC and the Peripheral DMA

– Three internal 1 Mbyte memory areas

– One 256 Mbyte embedded peripheral area

– Source, Type and all parameters of the access leading to an abort are saved

– Facilitates debug by detection of bad pointers

– Alignment checking of all data accesses

– Abort generation in case of misalignment

– Remaps the SRAM in place of the embedded non-volatile memory

– Allows handling of dynamic exception vectors

Controller

®

high-performance 32-bit instruction set

®

high code density 16-bit instruction set

6209DS–ATARM–17-Feb-09