PIC16F690DM-PCTLHS Microchip Technology, PIC16F690DM-PCTLHS Datasheet - Page 181

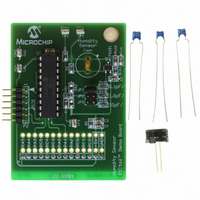

PIC16F690DM-PCTLHS

Manufacturer Part Number

PIC16F690DM-PCTLHS

Description

BOARD DEMO PICTAIL HUMIDITY SNSR

Manufacturer

Microchip Technology

Series

PICtail™r

Datasheets

1.PIC16F690DM-PCTLHS.pdf

(36 pages)

2.PIC16F690DM-PCTLHS.pdf

(32 pages)

3.PIC16F690DM-PCTLHS.pdf

(306 pages)

4.PIC16F690DM-PCTLHS.pdf

(14 pages)

Specifications of PIC16F690DM-PCTLHS

Sensor Type

Humidity

Sensing Range

1 ~ 99% RH

Interface

Analog

Voltage - Supply

5V

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP6291, PIC16F690

Processor To Be Evaluated

MCP6291 and PIC16F690

Interface Type

ICSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

AC162061 - HEADER INTRFC MPLAB ICD2 20PIN

Sensitivity

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

- PIC16F690DM-PCTLHS PDF datasheet

- PIC16F690DM-PCTLHS PDF datasheet #2

- PIC16F690DM-PCTLHS PDF datasheet #3

- PIC16F690DM-PCTLHS PDF datasheet #4

- Current page: 181 of 306

- Download datasheet (6Mb)

13.0

The Synchronous Serial Port (SSP) module is a serial

interface used to communicate with other peripheral or

microcontroller devices. These peripheral devices

may be serial EEPROMs, shift registers, display

drivers, A/D converters, etc. The SSP module can

operate in one of two modes:

• Serial Peripheral Interface (SPI)

• Inter-Integrated Circuit (I

Refer to Application Note AN578, “Use of the SSP

Module in the Multi-Master Environment” (DS00578).

13.1

This section contains register definitions and operational

characteristics of the SPI module.

The SPI mode allows 8 bits of data to be synchronously

transmitted and received simultaneously. To accomplish

communication, typically three pins are used:

• Serial Data Out (SDO)

• Serial Data In (SDI)

• Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave

mode of operation:

• Slave Select (SS)

© 2008 Microchip Technology Inc.

Note 1: When the SPI is in Slave mode with SS

2: If the SPI is used in Slave mode with

3: When the SPI is in Slave mode with SS

SSP MODULE OVERVIEW

SPI Mode

pin control enabled (SSPM<3:0> bits of

the SSPCON register = 0100), the SPI

module will reset if the SS pin is set to

V

CKE = 1, then the SS pin control must be

enabled.

pin control enabled (SSPM<3:0> bits of

the SSPCON register = 0100), the state

of the SS pin can affect the state read

back from the TRISC<4> bit. The

peripheral OE signal from the SSP

module into PORTC controls the state that

is read back from the TRISC<4> bit (see

Section 17.0

Specifications”

PORTC). If read-write-modify instructions,

such as BSF, are performed on the

TRISC register while the SS pin is high,

this will cause the TRISC<7> bit to be set,

thus disabling the SDO output.

DD

.

2

C

™

for

)

PIC16F631/677/685/687/689/690

information

“Electrical

on

FIGURE 13-1:

SDI/SDA

SCK/

SDO

SCL

SS

Peripheral OE

Read

SS Control

Select

TRISB<6>

Edge

bit 0

Enable

Select

Edge

SSPBUF Reg

SSP BLOCK DIAGRAM

(SPI MODE)

SSPSR Reg

SSPM<3:0>

Clock Select

4

2

DS41262E-page 179

Clock

Shift

Write

Prescaler

4, 16, 64

TMR2 Output

Data Bus

Internal

2

T

CY

Related parts for PIC16F690DM-PCTLHS

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: