CDB42448 Cirrus Logic Inc, CDB42448 Datasheet - Page 30

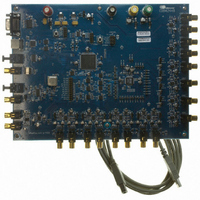

CDB42448

Manufacturer Part Number

CDB42448

Description

BOARD EVAL FOR CS42448 CODEC

Manufacturer

Cirrus Logic Inc

Specifications of CDB42448

Main Purpose

Audio, CODEC

Embedded

Yes, FPGA / CPLD

Utilized Ic / Part

CS42448

Primary Attributes

24-Bit, 192 kHz, 6 ADCs: 102dB Dynamic Range, 8 DACs: 105dB Dynamic Range

Secondary Attributes

Time Division Multiplexed (TDM), I2C, and SPI Interface, Popguard® Technology

Description/function

Audio CODECs

Operating Supply Voltage

5 V to 12 V

Product

Audio Modules

For Use With/related Products

CS42448

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Other names

598-1151

30

4.4

Sample Rate

Sample Rate

Sample Rate

System Clocking

The CODEC (ADC & DAC) serial audio interface ports operate either as a slave or master. The serial ports

accept externally generated clocks in slave mode and will generate synchronous clocks derived from an in-

put master clock in master mode. In the TDM format the ADC and DAC serial ports will only operate as a

slave. In OLM #2 the serial ports will accept or output a 256Fs SCLK. See the registers

Mode (DAC_FM[1:0])” on page 43

master/slave mode.

The CODEC requires external generation of the master clock (MCLK). The frequency of this clock must be

an integer multiple of, and synchronous with, the system sample rate, Fs.

The required integer ratios, along with some common frequencies, are illustrated in tables

The frequency range of MCLK must be specified using the MFREQ bits in register

(MFREQ[2:0])” on page

(kHz)

(kHz)

(kHz)

176.4

De-emphasis is only available in Single-Speed Mode. Please see

(DAC_DEM)” on page 46

44.1

88.2

192

32

48

64

96

11.2896

12.2880

Table 3. Double-Speed Mode Common Frequencies

8.1920

Table 2. Single-Speed Mode Common Frequencies

11.2896

12.2880

11.2896

12.2880

256x

8.1920

Table 4. Quad-Speed Mode Common Frequencies

128x

64x

43.

for de-emphasis control.

Figure 14. De-Emphasis Curve

-10dB

Gain

0dB

and

dB

12.2880

16.9344

18.4320

12.2880

16.9344

18.4320

“ADC Functional Mode (ADC_FM[1:0])” on page 43

16.9344

18.4320

384x

192x

96x

3.183 kHz

T1=50 µs

F1

MCLK (MHz)

MCLK (MHz)

MCLK (MHz)

16.3840

22.5792

24.5760

16.3840

22.5792

24.5760

10.61 kHz

512x

256x

22.5792

24.5760

128x

F2

T2 = 15 µs

Frequency

24.5760

33.8688

36.8640

24.5760

33.8688

36.8640

768x

33.8688

36.8640

384x

“DAC De-Emphasis Control

192x

“MCLK Frequency

“DAC Functional

Tables 2

for setting up

CS42448

32.7680

45.1584

49.1520

32.7680

45.1584

49.1520

45.1584

49.1520

1024x

512x

256x

DS648F3

to 4.