V2DIP1-48 FTDI, Future Technology Devices International Ltd, V2DIP1-48 Datasheet - Page 3

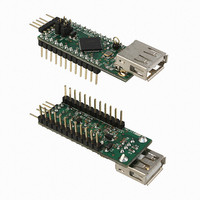

V2DIP1-48

Manufacturer Part Number

V2DIP1-48

Description

MOD MCU-USB HOST CTLR 24-DIP

Manufacturer

FTDI, Future Technology Devices International Ltd

Series

Vinculum-IIr

Datasheet

1.V2DIP1-48.pdf

(25 pages)

Specifications of V2DIP1-48

Main Purpose

Interface, USB 2.0 Host/Controller

Embedded

Yes, ASIC

Utilized Ic / Part

VNC2-48Q

Primary Attributes

Single A-Type Connector, UART / Parallel FIFO / SPI Interfaces

Secondary Attributes

Second USB Port is Available via Pins, Traffic LEDs

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

768-1057

1

2

3

4

5

6

7

8

3.1

3.2

3.3

3.4

3.5

3.6

3.7

3.8

3.9

4.1

4.2

4.3

5.1

Appendix A – References ............................................................................................ 22

Appendix B – List of Figures and Tables ................................................................... 23

List of Figures............................................................................................................... 23

List of Tables ................................................................................................................ 23

Appendix C – Revision History ................................................................................... 24

Introduction............................................................................................ 1

Features ................................................................................................. 3

Pin Out and Signal Description ............................................................ 4

3.5.1

3.6.1

3.6.2

3.7.1

3.7.2

3.8.1

3.9.1

Firmware .............................................................................................. 17

External circuit Configuration ............................................................ 18

Mechanical Dimensions ...................................................................... 19

Schematic Diagram ............................................................................. 20

Contact Information............................................................................. 21

Module Pin Out .................................................................................................... 4

Pin Signal Description ........................................................................................ 6

I/O Configuration Using The Jumper Pin Header ............................................. 8

Default Interface I/O Pin Configuration .............................................................. 9

UART Interface ................................................................................................... 10

Serial Peripheral Interface (SPI) ....................................................................... 11

Parallel FIFO Interface-Asynchronous Mode .................................................. 12

Parallel FIFO Interface-Synchronous Mode .................................................... 14

Debugger Interface ............................................................................................ 16

Firmware Support .............................................................................................. 17

Available Firmware ............................................................................................ 17

Firmware Upgrades ........................................................................................... 17

Adding a second USB Port ............................................................................... 18

Signal Description – UART Interface .............................................................................. 10

Signal Description - SPI Slave ........................................................................................ 11

Signal Description - SPI Master ...................................................................................... 11

Signal Description - Parallel FIFO Interface ................................................................. 12

Timing Diagram – Asynchronous FIFO Mode Read and Write Cycle ..................... 13

Timing Diagram – Synchronous FIFO Mode Read and Write Cycle ....................... 14

Signal Description - Debugger Interface ...................................................................... 16

Copyright © 2010 Future Technology Devices International Limited

`

Table of Contents

V2DIP1-48 VNC2-48 Development Module Datasheet Version 1.01

Document Reference No.: FT_000236

Clearance No.: FTDI# 153

2