HD6433045 HITACHI [Hitachi Semiconductor], HD6433045 Datasheet - Page 488

HD6433045

Manufacturer Part Number

HD6433045

Description

Hitachi Single-Chip Microcomputer

Manufacturer

HITACHI [Hitachi Semiconductor]

Datasheet

1.HD6433045.pdf

(867 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD6433045A58F

Manufacturer:

PWRT

Quantity:

4 172

Part Number:

HD6433045SA28FV

Manufacturer:

RENESAS/瑞萨

Quantity:

20 000

- Current page: 488 of 867

- Download datasheet (3Mb)

Transmitting and Receiving Data

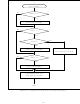

Transmitting Multiprocessor Serial Data: Figure 13-10 shows a sample flowchart for

transmitting multiprocessor serial data and indicates the procedure to follow.

Clear DR bit to 0, set DDR bit to 1

TDR and set MPBT bit in SSR

Figure 13-10 Sample Flowchart for Transmitting Multiprocessor Serial Data

Read TDRE flag in SSR

Read TEND flag in SSR

Clear TE bit to 0 in SCR

Write transmit data in

Clear TDRE flag to 0

Output break signal?

All data transmitted?

Start transmitting

TDRE = 1?

TEND = 1?

Initialize

End

Yes

Yes

Yes

Yes

No

No

No

No

477

1

2

3

4

1.

2.

3.

4.

SCI initialization: the transmit data

output function of the TxD pin is

selected automatically.

SCI status check and transmit data

write: read SSR, check that the TDRE

flag is 1, then write transmit

data in TDR. Also set the MPBT flag to

0 or 1 in SSR. Finally, clear the TDRE

flag to 0.

To continue transmitting serial data:

after checking that the TDRE flag is 1,

indicating that data can be

written, write data in TDR, then clear

the TDRE flag to 0. When the DMAC

is activated by a transmit-data-empty

interrupt request (TXI) to write data in

TDR, the TDRE flag is checked and

cleared automatically.

To output a break signal at the end of

serial transmission: set the DDR bit to

1 and clear the DR bit to 0 (DDR and

DR are I/O port registers), then clear

the TE bit to 0 in SCR.

Related parts for HD6433045

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

LOW FREQUENCY POWER AMPLIFIER

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON N-CHANNEL JUNCTION FET LOW FREQUECY LOW NOISE AMPLIFIER

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON SPEED POWER SWITCHING

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON P-CHANNEL MOS FET HIGH SPEED POWER SWITCHING

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON P-CHANNEL MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

SILICON P-CHANNEL MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet:

Part Number:

Description:

Silicon P-Channel MOS FET

Manufacturer:

HITACHI [Hitachi Semiconductor]

Datasheet: