PSMN3R5-80ES,127 NXP Semiconductors, PSMN3R5-80ES,127 Datasheet

PSMN3R5-80ES,127

Specifications of PSMN3R5-80ES,127

Related parts for PSMN3R5-80ES,127

PSMN3R5-80ES,127 Summary of contents

Page 1

... PSMN3R5-80ES N-channel 80 V, 3.5 mΩ standard level MOSFET in I2PAK Rev. 02 — 19 April 2011 1. Product profile 1.1 General description Standard level N-channel MOSFET in I2PAK package qualified to 175C. This product is designed and qualified for use in a wide range of industrial, communications and domestic equipment. ...

Page 2

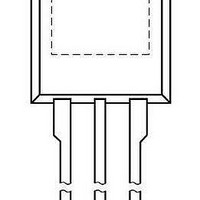

... N-channel 80 V, 3.5 mΩ standard level MOSFET in I2PAK Simplified outline SOT226 (I2PAK) Description plastic single-ended package (I2PAK); TO-262 All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES Graphic symbol mbb076 Version SOT226 © NXP B.V. 2011. All rights reserved ...

Page 3

... GS 003aaf615 120 P der (%) 150 200 0 ( ° Fig 2. Normalized total power dissipation as a function of mounting base temperature All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES Min - = 20 kΩ -20 [1] Figure 1 - [1] Figure ° -55 175 -55 175 - 260 ...

Page 4

... Safe operating area; continuous and peak drain currents as a function of drain-source voltage PSMN3R5-80ES Product data sheet N-channel 80 V, 3.5 mΩ standard level MOSFET in I2PAK = All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES 003aaf614 =10 μ 100 μ 100 ...

Page 5

... Transient thermal impedance from junction to mounting base as a function of pulse duration PSMN3R5-80ES Product data sheet N-channel 80 V, 3.5 mΩ standard level MOSFET in I2PAK Conditions see Figure 4 Vertical in free air - All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES Min Typ Max - 0.22 0. 003aaf613 tp P δ = ...

Page 6

... DS GS see Figure 14; see Figure see Figure 14; see Figure MHz °C; see Figure 0.53 Ω Ω G(ext) All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES Min Typ Max = -55 ° ° 4 0. 500 = 25 ° 100 - - 100 - 7.2 8 ...

Page 7

... C (pF) 12000 8000 4000 (V) GS Fig 8. Input and reverse transfer capacitances as a function of gate-source voltage; typical values All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES Min Typ = 25 ° 121 003aaf603 = 175 ° ° ...

Page 8

... GS 1 (V) DS Fig 10. Gate-source threshold voltage as a function of 03aa35 typ max (V) GS Fig 12. Normailzed drain-source on-state resistance All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES 5 GS(th) (V) 4 max 3 typ 2 min 1 0 − junction temperature 3 a 2.4 1 ...

Page 9

... N-channel 80 V, 3.5 mΩ standard level MOSFET in I2PAK 003aaf612 V (V) = 4.5 GS 5.5 6.0 20 (A) D Fig 14. Gate charge waveform definitions 003aaf609 120 160 Q (nC) G Fig 16. Input, output and reverse transfer capacitances All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES GS(pl) V GS(th GS1 GS2 G(tot ...

Page 10

... Fig 17. Source current as a function of source-drain voltage; typical values PSMN3R5-80ES Product data sheet N-channel 80 V, 3.5 mΩ standard level MOSFET in I2PAK ( 175 ° 0.25 0.5 0.75 All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES 003aaf611 = 25 ° (V) SD © NXP B.V. 2011. All rights reserved ...

Page 11

... max 0.7 1.6 10.3 11 2.54 0.4 1.2 9.7 REFERENCES JEDEC JEITA TO-262 All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES mounting base 15.0 3.30 2.6 13.5 2.79 2.2 EUROPEAN PROJECTION SOT226 ISSUE DATE 06-02-14 09-08-25 © ...

Page 12

... NXP Semiconductors 8. Revision history Table 7. Revision history Document ID Release date PSMN3R5-80ES v.2 20110419 • Modifications: Status changed from objective to product. • Various changes to content. PSMN3R5-80ES v.1 20101224 PSMN3R5-80ES Product data sheet N-channel 80 V, 3.5 mΩ standard level MOSFET in I2PAK Data sheet status ...

Page 13

... Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device. All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES © NXP B.V. 2011. All rights reserved ...

Page 14

... TrenchMOS, TriMedia and UCODE — are trademarks of NXP B.V. HD Radio and HD Radio logo — are trademarks of iBiquity Digital Corporation. http://www.nxp.com salesaddresses@nxp.com All information provided in this document is subject to legal disclaimers. Rev. 02 — 19 April 2011 PSMN3R5-80ES Trademarks © NXP B.V. 2011. All rights reserved ...

Page 15

... Please be aware that important notices concerning this document and the product(s) described herein, have been included in section ‘Legal information’. © NXP B.V. 2011. For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com All rights reserved. Date of release: 19 April 2011 Document identifier: PSMN3R5-80ES ...