DP83256VF National Semiconductor, DP83256VF Datasheet - Page 103

DP83256VF

Manufacturer Part Number

DP83256VF

Description

IC FDDI LAYER CTRLR 160PQFP

Manufacturer

National Semiconductor

Series

PLAYER+™r

Datasheet

1.DP83256VF.pdf

(144 pages)

Specifications of DP83256VF

Controller Type

physical layer controller

Voltage - Supply

4.75 V ~ 5.25 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

160-BFQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Current - Supply

-

Interface

-

Other names

*DP83256VF

- Current page: 103 of 144

- Download datasheet (997Kb)

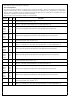

PMID

PMID

RXC OUT

RXC OUT

RXD OUT

RXD OUT

RXC IN

RXC IN

RXD IN

RXD IN

PMRD

PMRD

TXC

TXC

SD

SD

TEL

TXE

6 0 Signal Descriptions

Alternate PMD Interface

Symbol

b

a

a

b

a

b

b

a

a

b

b

a

b

b

a

a

Pin

62

61

56

55

83

82

76

75

78

77

54

53

51

50

60

59

74

73

I O

O

O

O

O

O

I

I

I

I

I

PMD Indicate Data Differential 100k ECL 125 Mbps serial data input signals from the PMD

Receiver into the Clock Recovery Module (CRM) of the PLAYER

Recovered Clock Out 125 MHz clock recovered by the Clock Recovery Module (CRM) from the

PMID data input

These signals are only active when the Alternate PMD Enable (APMDEN) bit of the Alternate PMD

Register (APMDREG) is set to a 1 and are off by default after Reset

When these two pins are not used they should be left Not Connected (N C)

Recovered Data Out 125 Mbps data recovered by the Clock Recovery Module (CRM) from the

PMID data input

These signals are only active when the Alternate PMD Enable (APMDEN) bit of the Alternate PMD

Register (APMDREG) is set to a 1 and are off by default after Reset

When these two pins are not used they should be left Not Connected (N C)

Receive Clock In Clock inputs to the Player section of the PLAYER

synchronized with the RXD IN inputs

These signals are only active when the Alternate PMD Enable (APMDEN) bit of the Alternate PMD

Register (APMDREG) is set to a 1 and are off by default after Reset

When these two pins are not used pin 76 should be left Not Connected (N C) and pin 75 should be

connected directly to ground (Reserved 0)

Receive Data In Data inputs to the Player section of the PLAYER

synchronized with the RXC IN inputs

These signals are only active when the Alternate PMD Enable (APMDEN) bit of the Alternate PMD

Register (APMDREG) is set to a 1 and are off by default after Reset

When these two pins are not used pin 78 should be left Not Connected (N C) and pin 77 should be

connected directly to ground (Reserved 0)

PMD Request Data Differential 100k ECL 125 Mbps serial data output signals to the PMD

transmitter

Transmit Clock 125 MHz 100k ECL compatible differential outputs synchronized to the outgoing

PMRD data

These signals can be enabled using the Transmit Clock Enable (TXCE) bit in the Clock Generation

Module Register (CGMREG)

When these two pins are not used they should be left Not Connected (N C)

Signal Detect Differential 100k ECL input signals from the PMD receiver indicating that a signal

is being received by the PMD receiver

PMD Transmitter Enable Level A TTL input signal to select the PMD transmitter Enable (TXE)

signal level

PMD Transmitter Enable A TTL output signal to enable disable the PMD transmitter The output

level of the TXE pin is determined by three parameters the Transmit Enable (TE) bit in the Mode

Register the TM2–TM0 bits in the Current Transmit State Register and the input to the TEL pin

The following rules summarize the output of the TXE pin

1 If TE

2 If TE

3 If TE

4 If TE

5 If TE

6 If TE

e

e

e

e

e

e

(Continued)

0 and TEL

0 and TEL

1 and OTM and TEL

1 and OTM and TEL

1 and not OTM and TEL

1 and not OTM and TEL

e

e

GND then TXE

V

CC

then TXE

e

e

103

GND then TXE

V

CC

e

e

GND then TXE

V

e

then TXE

CC

e

GND

V

then TXE

CC

Description

e

e

GND

V

e

CC

e

V

GND

CC

a

a

a

These inputs must be

These inputs must be

Related parts for DP83256VF

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

National Semiconductor [8-Bit D/A Converter]

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

National Semiconductor [Media Coprocessor]

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Digitally Controlled Tone and Volume Circuit with Stereo Audio Power Amplifier, Microphone Preamp Stage and National 3D Sound

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Digitally Controlled Tone and Volume Circuit with Stereo Audio Power Amplifier, Microphone Preamp Stage and National 3D Sound

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

AC97 Rev 2 Codec with Sample Rate Conversion and National 3D Sound

Manufacturer:

National Semiconductor

Part Number:

Description:

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

General Purpose, Low Voltage, Low Power, Rail-to-Rail Output Operational Amplifiers

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

8-bit 20 MSPS flash A/D converter.

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Low Noise Quad Operational Amplifier

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Quad Differential Line Receivers

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Quad High Speed Trapezoidal? Bus Transceiver

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Dual Line Receiver

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

TTL to 10k ECL Level Translator with Latch

Manufacturer:

National Semiconductor

Datasheet: