DS31412N Maxim Integrated Products, DS31412N Datasheet - Page 72

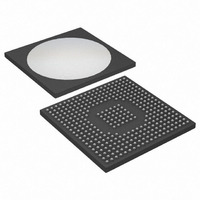

DS31412N

Manufacturer Part Number

DS31412N

Description

IC 12CH DS3/3 FRAMER 349-BGA

Manufacturer

Maxim Integrated Products

Datasheet

1.DS3148.pdf

(89 pages)

Specifications of DS31412N

Controller Type

DS3/E3 Framer

Interface

LIU

Voltage - Supply

3.135 V ~ 3.465 V

Current - Supply

960mA

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

349-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Exit2-DR. While in this state, a rising edge on JTCLK with JTMS high puts the controller in the Update-DR state

and terminates the scanning process. A rising edge on JTCLK with JTMS low puts the controller in the Shift-DR

state.

Update-DR. A falling edge on JTCLK while in the Update-DR state latches the data from the shift register path of

the test registers into the data output latches. This prevents changes at the parallel output because of changes in

the shift register. A rising edge on JTCLK with JTMS low puts the controller in the Run-Test-Idle state. With JTMS

high, the controller enters the Select-DR-Scan state.

Select-IR-Scan. All test registers retain their previous state. The instruction register remains unchanged during this

state. With JTMS low, a rising edge on JTCLK moves the controller into the Capture-IR state and initiates a scan

sequence for the instruction register. JTMS high during a rising edge on JTCLK puts the controller back into the

Test-Logic-Reset state.

Capture-IR. The Capture-IR state is used to load the shift register in the instruction register with a fixed value. This

value is loaded on the rising edge of JTCLK. If JTMS is high on the rising edge of JTCLK, the controller enters the

Exit1-IR state. If JTMS is low on the rising edge of JTCLK, the controller enters the Shift-IR state.

Shift-IR. In this state, the shift register in the instruction register is connected between JTDI and JTDO and shifts

data one stage for every rising edge of JTCLK toward the serial output. The parallel register and all test registers

remain at their previous states. A rising edge on JTCLK with JTMS high moves the controller to the Exit1-IR state.

A rising edge on JTCLK with JTMS low keeps the controller in the Shift-IR state while moving data one stage

through the instruction shift register.

Exit1-IR. A rising edge on JTCLK with JTMS low puts the controller in the Pause-IR state. If JTMS is high on the

rising edge of JTCLK, the controller enters the Update-IR state and terminates the scanning process.

Pause-IR. Shifting of the instruction register is halted temporarily. With JTMS high, a rising edge on JTCLK puts

the controller in the Exit2-IR state. The controller remains in the Pause-IR state if JTMS is low during a rising edge

on JTCLK.

Exit2-IR. A rising edge on JTCLK with JTMS high puts the controller in the Update-IR state. The controller loops

back to the Shift-IR state if JTMS is low during a rising edge of JTCLK in this state.

Update-IR. The instruction shifted into the instruction shift register is latched into the parallel output on the falling

edge of JTCLK as the controller enters this state. Once latched, this instruction becomes the current instruction. A

rising edge on JTCLK with JTMS low puts the controller in the Run-Test-Idle state. With JTMS high, the controller

enters the Select-DR-Scan state.

9.2 JTAG Instruction Register and Instructions

The instruction register contains a shift register as well as a latched parallel output and is 3 bits in length. When the

TAP controller enters the Shift-IR state, the instruction shift register is connected between JTDI and JTDO. While in

the Shift-IR state, a rising edge on JTCLK with JTMS low shifts data one stage toward the serial output at JTDO. A

rising edge on JTCLK in the Exit1-IR state or the Exit2-IR state with JTMS high moves the controller to the Update-

IR state. The falling edge of that same JTCLK latches the data in the instruction shift register to the instruction

parallel output.

codes.

Table 9-A. JTAG Instruction Codes

SAMPLE/PRELOAD

INSTRUCTIONS

BYPASS

EXTEST

IDCODE

CLAMP

HIGHZ

Table 9-A

shows the instructions supported by the device and their respective operational binary

SELECTED REGISTER

Device Identification

Boundary Scan

Boundary Scan

Bypass

Bypass

Bypass

72 of 89

INSTRUCTION CODES

010

111

000

011

100

001