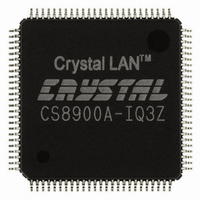

CS8900A-IQ3Z Cirrus Logic Inc, CS8900A-IQ3Z Datasheet - Page 93

CS8900A-IQ3Z

Manufacturer Part Number

CS8900A-IQ3Z

Description

IC LAN ETHERNET CTLR 3V 100LQFP

Manufacturer

Cirrus Logic Inc

Type

Single Chipr

Specifications of CS8900A-IQ3Z

Package / Case

100-LQFP

Controller Type

Ethernet Controller (IEEE 802.3)

Interface

ISA-BUS

Voltage - Supply

3V, 5V

Current - Supply

95mA

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Ethernet Connection Type

10BASE- 2 or 10BASE- 5 or 10BASE- F or 10BASE- T

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Product

Ethernet Controllers

Standard Supported

IEEE 802.3

Data Rate

10 Mbps

Supply Voltage (max)

6 V

Supply Voltage (min)

- 0.3 V

Supply Current (max)

+/- 10 mA

Maximum Operating Temperature

+ 85 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1163 - KIT EVAL FOR CS8900A

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

598-1129

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CS8900A-IQ3Z

Manufacturer:

Cirrus Logic Inc

Quantity:

1 852

Company:

Part Number:

CS8900A-IQ3Z

Manufacturer:

CIRRUS42

Quantity:

921

Company:

Part Number:

CS8900A-IQ3Z

Manufacturer:

Cirrus Logic Inc

Quantity:

10 000

Part Number:

CS8900A-IQ3Z

Manufacturer:

CIRRUS

Quantity:

20 000

Company:

Part Number:

CS8900A-IQ3ZR

Manufacturer:

Cirrus Logic Inc

Quantity:

10 000

DS271F5

be completely received. Usually, the DMA re-

ceive frame interrupt (RxDMAiE, bit 7, Regis-

ter B, BufCFG) is set so that the CS8900A

generates an interrupt when a frame is trans-

ferred by DMA. Figure 25 shows how a DMA

Receive Frame interrupt is processed.

In the interrupt service routine, the BufEvent

register (register C), bit RxDMA Frame (bit 7)

indicates that one or more receive frames

were transferred using DMA. The software

driver

PDMA_START) that will point to the beginning

of a new frame. After the CS8900A is initial-

ized and before any frame is received, pointer

PDMA_START points to the beginning of the

DMA buffer memory area. The first read of the

CS8900A

Crystal LAN™ Ethernet Controller

"Holes" due to

should

Base Address

double-word

DMA Buffer

alignment

maintain

a

Figure 24. Example of Frames Stored in DMA

CIRRUS LOGIC PRODUCT DATASHEET

pointer

RxStatus - Frame 1

(e.g.

RxLength - Frame 1

RxStatus - Frame 3

RxLength - Frame 3

RxStatus - Frame 2

RxLength - Frame 2

Frame 3

Frame 1

DMA Frame Count, CDMA, commits the mem-

ory covered by the CDMA count, and the DMA

cannot overwrite this committed space until

the space is freed. The driver then processes

the frames described by the CDMA count and

makes a second read of the DMA frame count.

This second read frees the buffer memory

space described by the CDMA counter.

During the frame processing, the software

should advance the PDMA_START pointer. At

the end of processing a frame, pointer

PDMA_START should be made to align with a

double-word boundary. The software remains

in the loop until the DMA frame count read is

zero.

Frame 2

register (PacketPage

DMA Start of Frame

base + 0126H)

points here.

(PacketPage base + 012Ah)

DMA Byte Count

93