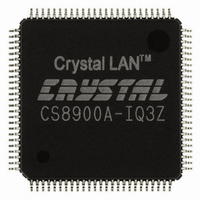

CS8900A-IQ3Z Cirrus Logic Inc, CS8900A-IQ3Z Datasheet - Page 68

CS8900A-IQ3Z

Manufacturer Part Number

CS8900A-IQ3Z

Description

IC LAN ETHERNET CTLR 3V 100LQFP

Manufacturer

Cirrus Logic Inc

Type

Single Chipr

Specifications of CS8900A-IQ3Z

Package / Case

100-LQFP

Controller Type

Ethernet Controller (IEEE 802.3)

Interface

ISA-BUS

Voltage - Supply

3V, 5V

Current - Supply

95mA

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Ethernet Connection Type

10BASE- 2 or 10BASE- 5 or 10BASE- F or 10BASE- T

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Product

Ethernet Controllers

Standard Supported

IEEE 802.3

Data Rate

10 Mbps

Supply Voltage (max)

6 V

Supply Voltage (min)

- 0.3 V

Supply Current (max)

+/- 10 mA

Maximum Operating Temperature

+ 85 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1163 - KIT EVAL FOR CS8900A

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

598-1129

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CS8900A-IQ3Z

Manufacturer:

Cirrus Logic Inc

Quantity:

1 852

Company:

Part Number:

CS8900A-IQ3Z

Manufacturer:

CIRRUS42

Quantity:

921

Company:

Part Number:

CS8900A-IQ3Z

Manufacturer:

Cirrus Logic Inc

Quantity:

10 000

Part Number:

CS8900A-IQ3Z

Manufacturer:

CIRRUS

Quantity:

20 000

Company:

Part Number:

CS8900A-IQ3ZR

Manufacturer:

Cirrus Logic Inc

Quantity:

10 000

Disable Backoff

FDX

At reset, if no EEPROM is found by the CS8900A, then the register has the following initial state. If an EEPROM is

found, then the register’s initial value may be set by the EEPROM. See Section 3.3 on page 19.

Reset value is: 0000 0000 0001 1001

4.4.23 Register 1C: AUI Time Domain Reflectometer

(Read-only, Address: PacketPage base + 013Ch)

The TDR counter (Bits 6 through F) is a time domain reflectometer useful in locating cable faults in 10BASE-2 and

10BASE-5 coax networks. It counts at a 10 MHz rate from the beginning of transmission on the AUI to when a col-

lision or Loss-of-Carrier error occurs. The TDR counter is cleared when read.

011100

AUI-Delay

Reset value is: 0000 0000 0001 1100

68

7

F

AUI Delay

of the inter packet gap before starting transmission. When clear, the backoff algorithm is used.

nored. This bit must be set when performing loopback tests on the 10BASE-T port. When clear,

the CS8900A is configured for standard half-duplex 10BASE-T operation.

Register. When reading this register, these bits will be 011100, where the LSB corresponds to

Bit 0.

transmission on the AUI to when a collision or Loss-of-Carrier error occurs.

When set, the backoff algorithm is disabled. The CS8900A transmitter looks only for completion

When set, 10BASE-T full duplex mode is enabled and CRS (Register 14, LineST, Bit E) is ig-

These bits provide an internal address used by the CS8900A to identify this as the Bus Status

The upper ten bits contains the number of 10 MHz clock periods between the beginning of

E

6

D

5

CIRRUS LOGIC PRODUCT DATASHEET

C

4

AUI Delay

B

3

011100

Crystal LAN™ Ethernet Controller

A

2

1

9

CS8900A

DS271F5

0

8