20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 95

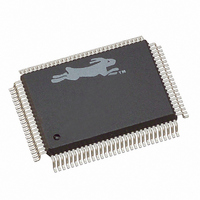

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 95 of 228

- Download datasheet (2Mb)

Serial Port A is selected for bootstrap operation as a clocked serial port when SMODE =

10. In this case bit 7 of Parallel Port C is used for the serial data and bit 1 of Parallel Port B

is used for the serial clock. Note that the serial clock must be externally supplied for boot-

strap operation. This precludes the use of a serial EEPROM for bootstrap operation.

Serial Port A is selected for bootstrap operation as an asynchronous serial port when

SMODE = 11. In this case bit 7 of Parallel Port C is used for the serial data and the 32 kHz

oscillator is used to provide the serial clock. A dedicated divide circuit allows the use of

the 32 kHz signal to provide the timing reference for the 2400 bps asynchronous transfer.

Only 2400 bps is supported for bootstrap operation, and the serial data must be eight bits

for proper operation.

When the first phase of a bootstrap is performed using Serial Port A, the TXA signal is not

needed since the bootstrap is a one-way communication. After the reset ends and the boot-

strap mode begins, TXA will be low, reflecting its function as a parallel port output bit that

is cleared by the reset. This may be interpreted as a break signal by some serial communi-

cation devices. TXA can be forced high by sending the triplet 0x80, 0x50, 0x40, which

stores 0x40 in parallel port C. An alternate approach is to send the triplet 0x80, 0x55,

0x40, which will enable the TXA output from bit 6 of parallel port C by writing to the par-

allel port C function register (0x55).

The transfer rate in any bootstrap operation must not be too fast for the processor to exe-

cute the instruction stream. The Write Empty signal acts as an interlock when using the

Slave Port for bootstrap operation, because the next byte should not be written to the Slave

Port until the Write Empty signal is active. No such interlock exists for the clocked serial

and asynchronous bootstrap operation. In these cases, remember that the processor clock

starts out in divide-by-eight mode with four wait states, and limit the transfer rate accord-

ingly. In asynchronous mode at 2400 bps it takes about 4 ms to send each character, so no

problem is likely unless the system clock is extremely slow.

Chapter 7 Miscellaneous I/O Functions

NOTE:

procedure, sending the “byte triplets,” two-way communication is required once

the cold loader has been loaded.

Although the TXA signal is not needed during the first phase of the boot

89

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: