20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 177

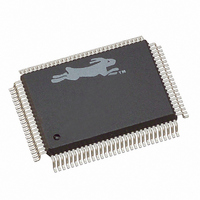

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 177 of 228

- Download datasheet (2Mb)

17.3 Shadow Registers

Many of the registers of the Rabbit’s internal I/O devices are write-only. This saves gates

on the chip, making possible greater capability at lower cost. Write-only registers are eas-

ier to use if a memory location, called a shadow register, is associated with each write-

only register. To make shadow register names easy to remember, the word shadow is

appended to the register name. For example the register GOCR (Global Output Control

register) has the shadow

source code as shown below.

If the port is a write-only port, the shadow register can be used to find out the port’s con-

tents. For example GCSR has a number of write-only bits. These can be read by consult-

ing the shadow, provided that the shadow register is always updated when writing to the

register.

17.3.1 Updating Shadow Registers

If the address of a shadow register is passed as an argument to one of the functions that

write to the internal or external I/O registers, then the shadow register will be updated as

well as the specified I/O register.

A

and

to the shadow register is mandatory for

17.3.2 Interrupt While Updating Registers

When manipulating I/O registers and shadow registers, the programmer must keep in

mind that an interrupt can take place in the middle of the sequence of operations, and then

the interrupt routine may manipulate the same registers. If this possibility exists, then a

solution must be crafted for the particular situation. Usually it is not necessary to disable

the interrupts while manipulating registers and their associated shadow registers.

17.3.2.1 Atomic Instruction

As an example, consider the parallel port D data direction register (PDDDR). This register

is write only, and it contains 8 bits corresponding to the 8 I/O pins of parallel port D. If a

bit in this register is a “1,” the corresponding port pin is an output, otherwise it is an input.

It is easy to imagine a situation where different parts of the application, such as an inter-

rupt routine and a background routine, need to be in charge of different bits in the PDDDR

register. The following code sets a bit in the shadow and then sets the I/O register. If an

interrupt takes place between the

PDDDR, the correct value will still be set in PDDDR.

Chapter 17 Other Rabbit Software

NULL

WrPortE()

char GCSRShadow; // Global Control Status Register

char GOCRShadow; // Global Output Control Registe

char GCDRShadow; // Global Clock Doubler Register

k=GCSRShadow;

pointer may replace the pointer to a shadow register as an argument to

; the shadow register associated with the port will not be updated. A pointer

GOCRShadow

set

and the

. Some shadow registers are defined in the BIOS

BitWrPortI()

ldd

, and changes the shadow register and

and

BitWrPortE()

r

WrPortI()

.

171

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: